## Bonding and CMP

Victor Ovchinnikov

Chapters 16, 17

#### **Previous lecture**

- Selective doping:

- diffusion

- ion implantation

- Epitaxy

#### **Next lecture**

• Integration

#### Outlook

- Bonding in general

- Bonding methods

- CMP

- Etching vs. CMP

#### Wafer bonding

- It is wafer-level permanent connection technology, ensuring mechanically stable and hermetically sealed assembling

- Bonding of blank and patterned wafers

- Wafer size 100 300 mm

- Back end of line (BEOL) process

## Wafer bonding applications

- Advanced substrates SOI

- Packaging

- Capping/Encapsulation

- Multi layer devices

- 3D structures

- Layer transfer

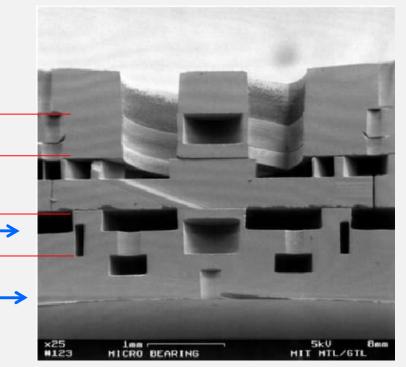

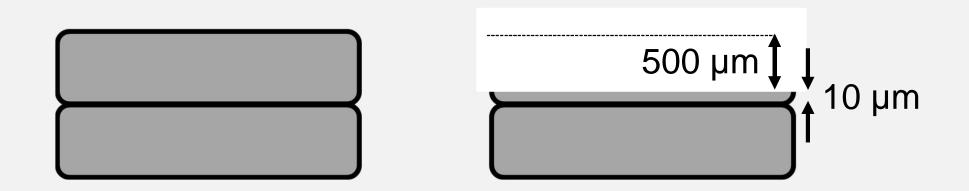

5 wafers, 380 µm each No wafer thinning Bonding – one at a time

#### Wire bonding Flip chip bonding \_\_\_\_\_\_ Not part of this course

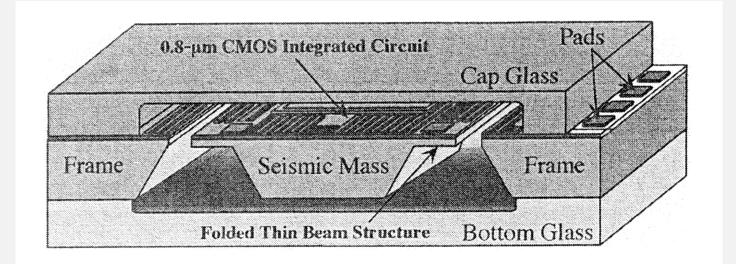

#### Accelerometer (glass-Si-glass) Capping/Encapsulation application

Anodic bonding: silicon-to-glass. Twice

Hermetic cavity (vacuum)

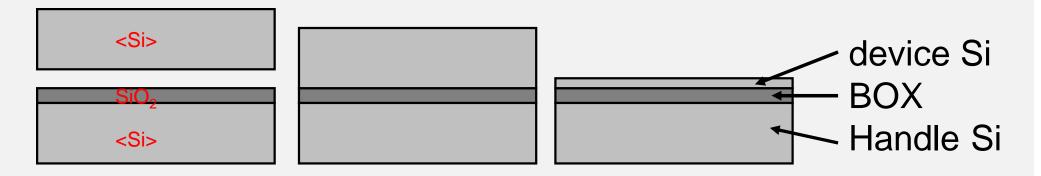

## SOI wafer fabrication

Advanced substrates application

#### Basic requirements for bonding

Wafers are flat (no centimeter scale wavyness) Wafers are smooth (atomic/micrometer scale), RMS=0.5 nm Materials form chemical bonds across the interface No high stress No interface bubbles

BOX= buried oxide

#### Why SOI wafers ?

#### CMOS

-easy isolation of transistors

-fewer process steps

-elimination of substrate effects

➔ faster transistors

-easy etch stop

- -single crystal material superior

- -device and handle silicon optimized separately

#### Why not SOI ? -> Expensive

## Bonding process steps

- -particle removal

- -chemical surface modification

- -(optional) vacuum pumping

- -(optional) wafer alignment

- -room temperature joining

- -application of force/heat/voltage

- -(optional) wafer thinning

#### **Bonding techniques**

- silicon direct bonding (SDB) = fusion bonding (FB): (Si/Si or SiO<sub>2</sub>/Si or SiO<sub>2</sub>/SiO<sub>2</sub>)

- anodic bonding (AB) = field assisted thermal bonding (FATB): Si/glass, glass/Si/glass

- thermo-compression bonding (TCB): Au-Au

- eutectic bonding: Si/Au (363 °C)

- adhesive bonding, "glueing": Si/polymer/Si

- glass frit bonding:

- Si, glass, SiO<sub>2</sub>, Al, Ti

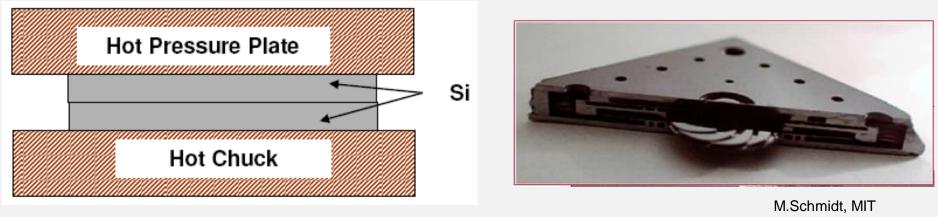

## Direct (fusion) bonding

- surface cleaning in RCA-1 (NH<sub>4</sub>OH-H<sub>2</sub>O<sub>2</sub>)->Si-OH

- room temperature joining

- initiation of bonding at centre or wafer flat

- anneal for bond energy improvement 1000°C or 400°C

- further processing with some limitations:

gases in cavities expand

thin membranes bend

bonded wafer stack is thicker than usual

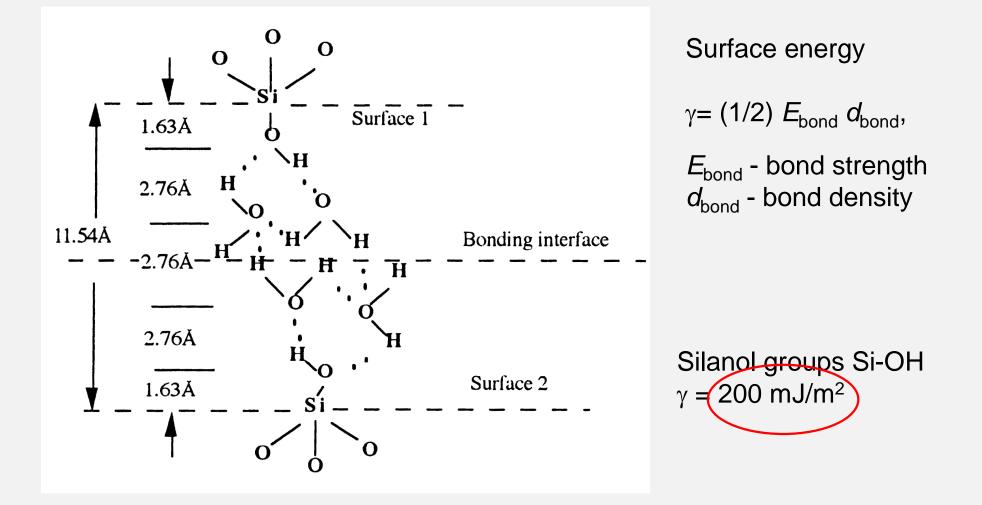

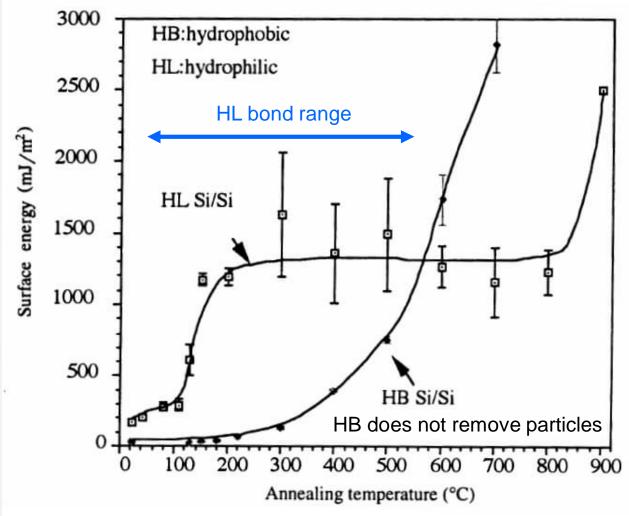

#### Bonding of hydrophylic Si surfaces: low temperature, low strength

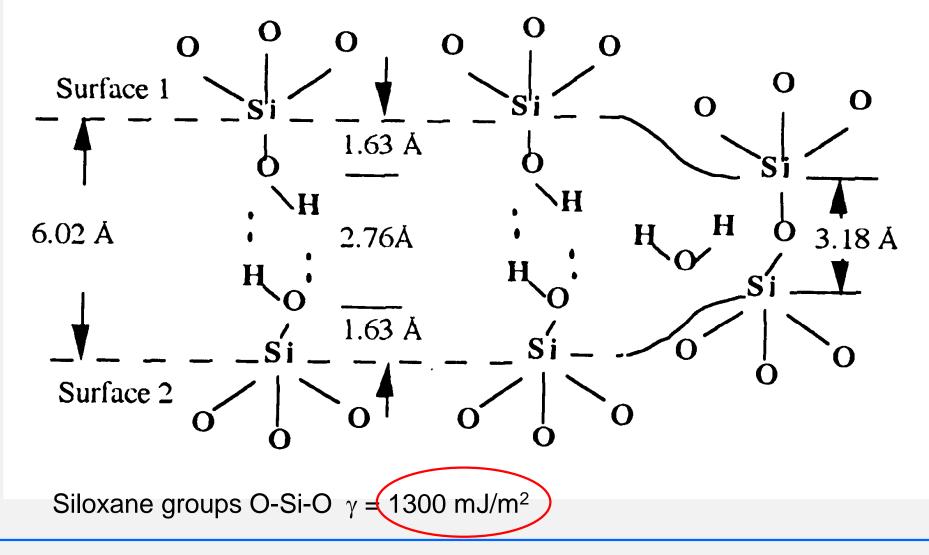

# A H<sub>2</sub>O removing and siloxane bond formation: high temperature, high strength

#### **Bond strength**

Tong & Gösele: Semiconductor wafer bonding

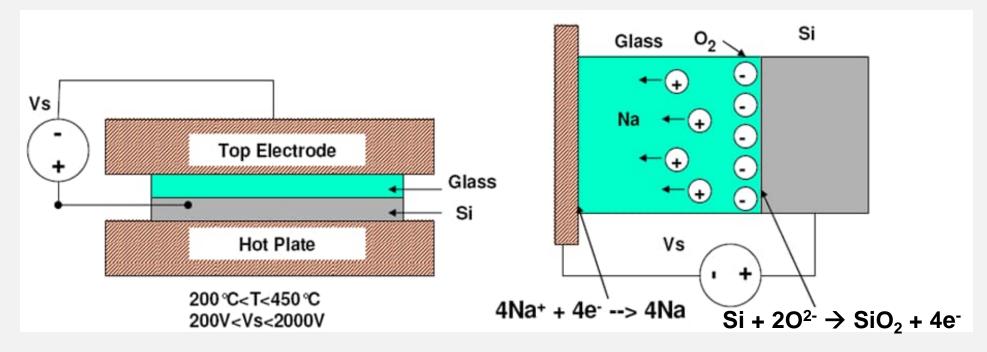

#### Anodic bonding

- 1. Limited number of glasses can be used (CTE problem), e.g. Pyrex 7740

- 2. Surface cleaning to remove particles. Native oxide, thin metal are not a problem

- 3. Pump to vacuum, heating, alignment

- 4. Mechanical contact and applying voltage

- 5. Electrostatic force pull wafers together and SiO<sub>2</sub> bonds are created

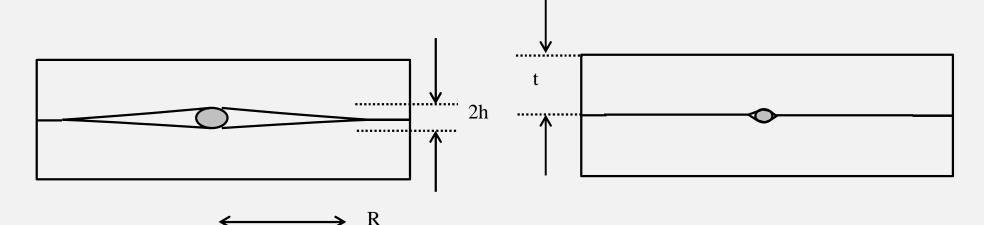

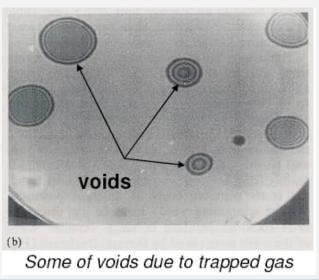

#### Interface particles and bubbles

Voids created by particles are very large compared to particles themselves because silicon is rigid material

#### Problems with trapped gas

Silicon can conform only to

#### very small particles, < 100 nm

S. Franssila presentation, Microsyste tech., 2006

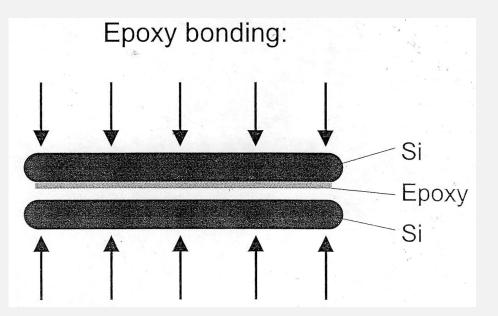

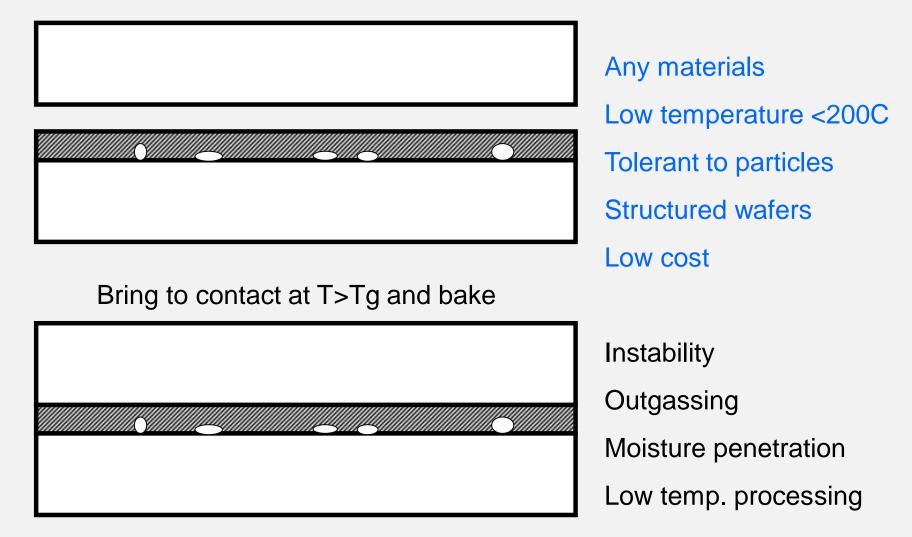

#### Glass frit and adhesive bonding

Rough surfaces High strength No outgassing Si, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, AI, Ti, glass Pattern by screen printing

Glass frit bonding:

450°C

Rough surfaces Low temperature Outgassing Pattern by screen printing

200°C

#### Adhesive bonding

Deposit adhesive polymer on wafer

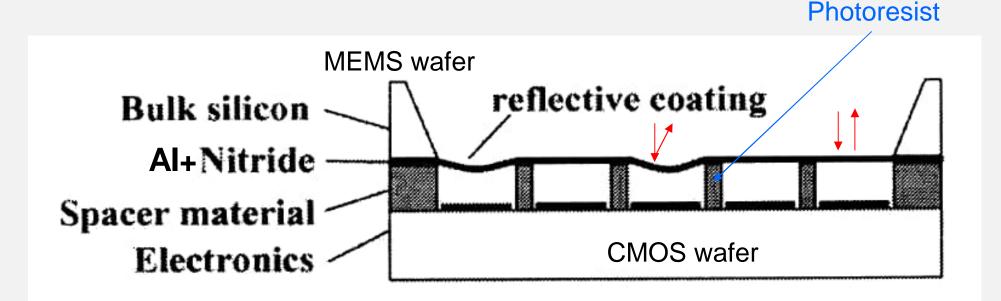

## Adhesive bonding of patterned wafers

Aluminium mirror on nitride membrane

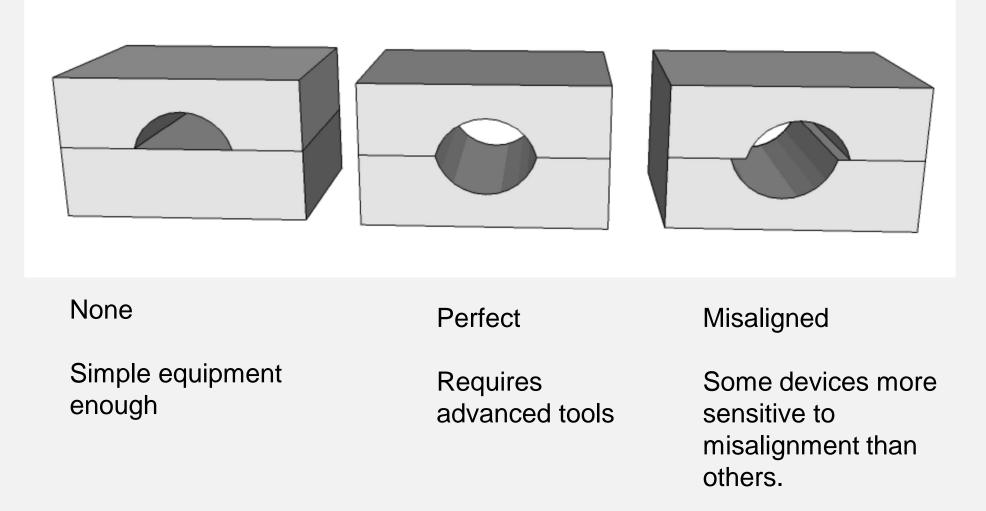

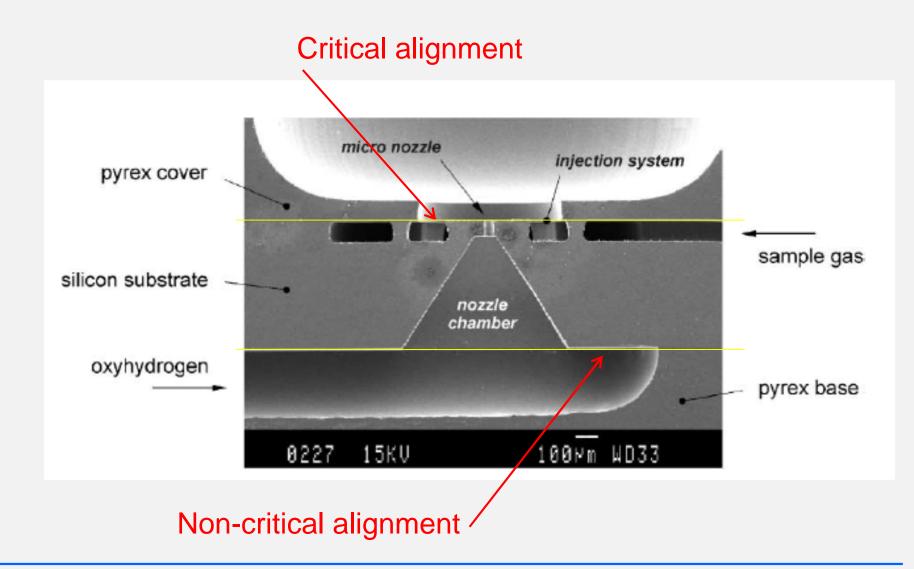

#### Bond alignment I

## Summary I

Bonding provides vertical integration of separately processed substrates

• High quality bonding can be done for limited range of materials and at elevated temperature

Bonding is VERY sensitive to surface preparation – particles, chemical bonds etc

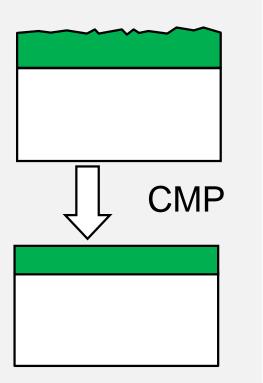

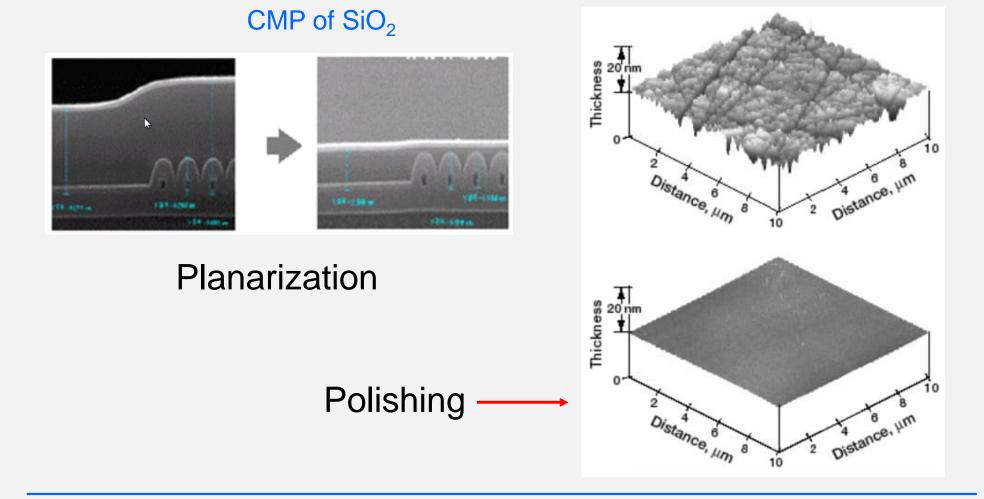

#### **Chemical mechanical planarization**

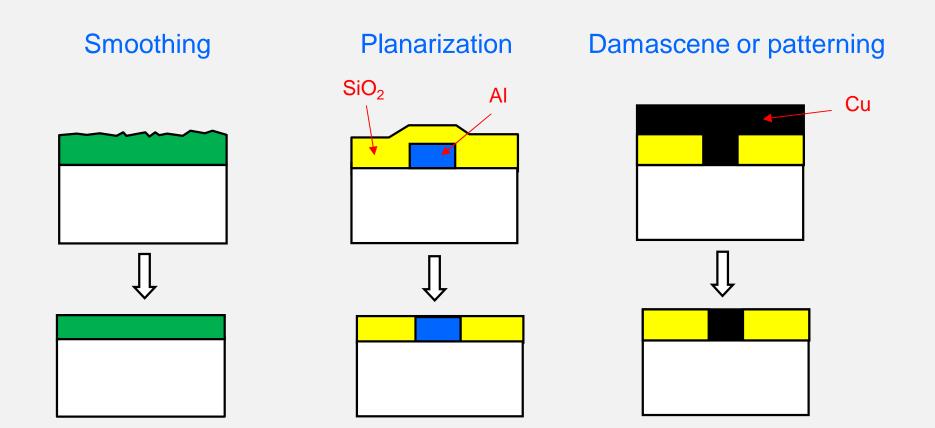

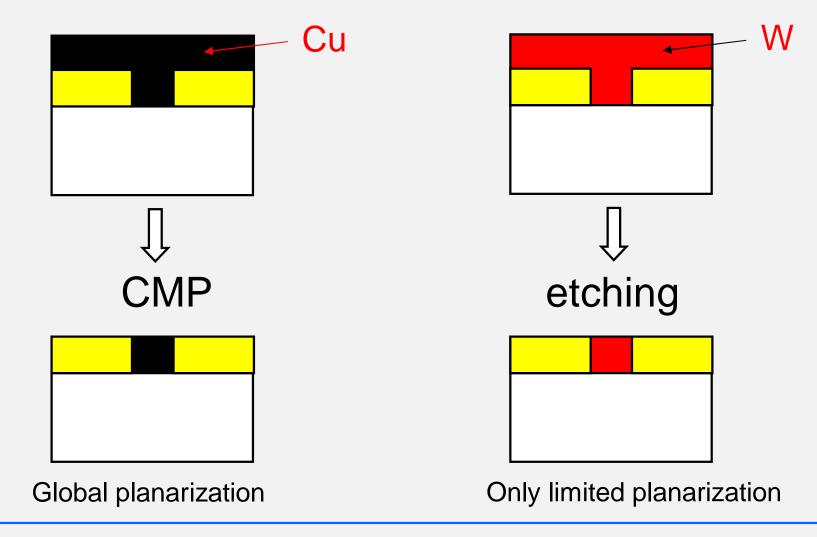

Chemical Mechanical Planarization (CMP) combines chemical action with mechanical abrasion to achieve selective material removal through polishing

• CMP achieves the greatest degree of planarization of any currently known technique

#### **Applications of CMP**

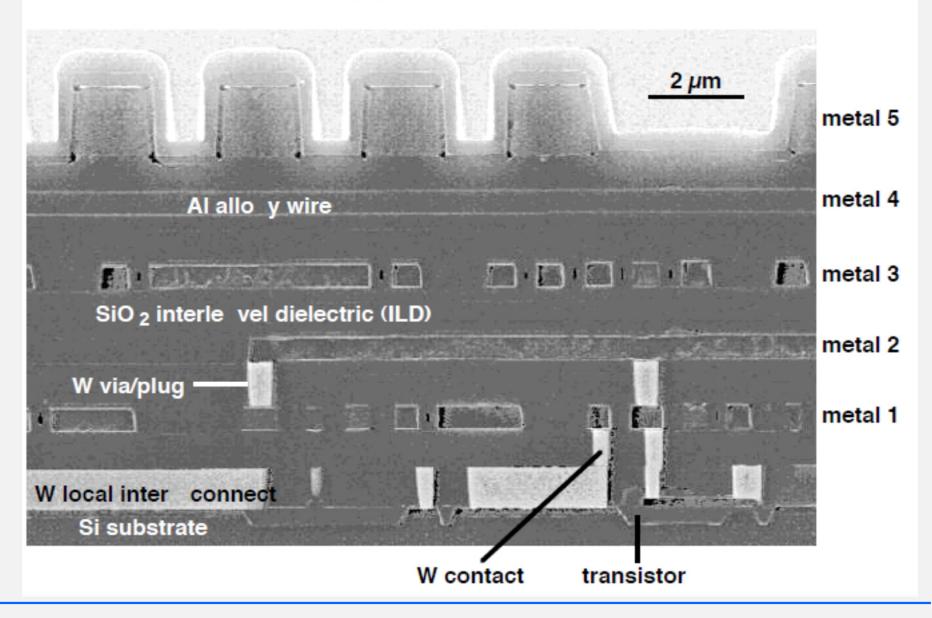

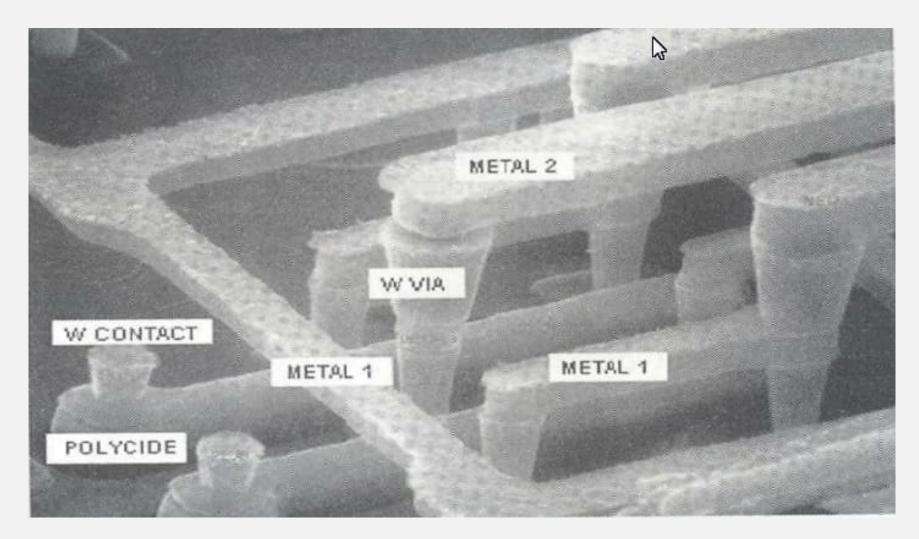

#### A Motorola µprocessor with 5 Al layers

#### Multilayer processing by CMP

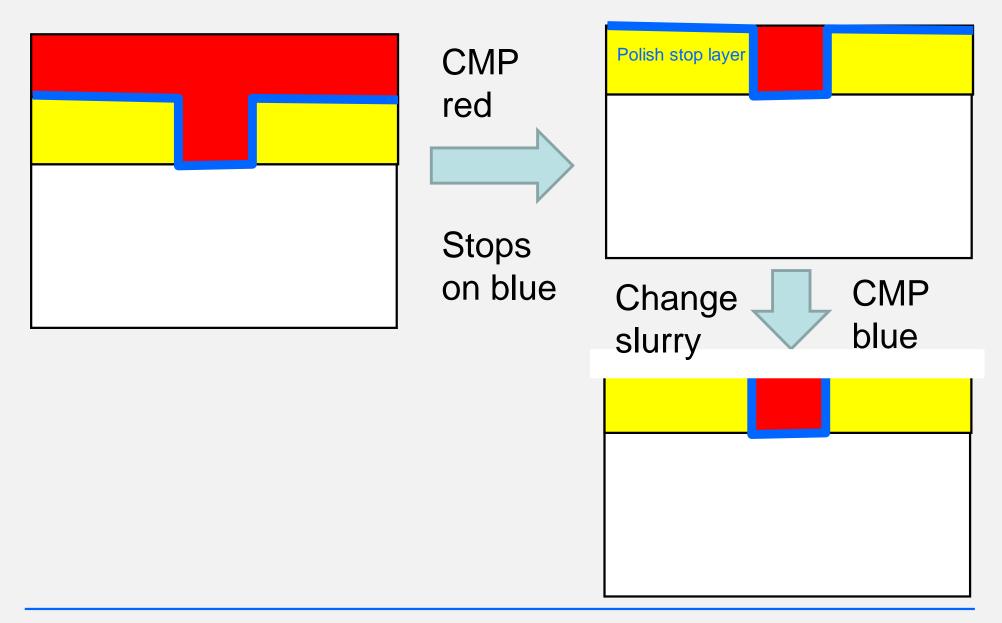

#### Polish selectivity & polish stop

Polish selectivity:

Polishing rate of material 1 / polishing rate of material 2

e.g. Copper 400 nm/min Oxide 40 nm/min -> 10:1 e.g. Copper 400 nm/min TaN 10 nm/min → 40:1

Polish stop: if selectivity is very high, we call it polish stop (even though some underlying material is removed)

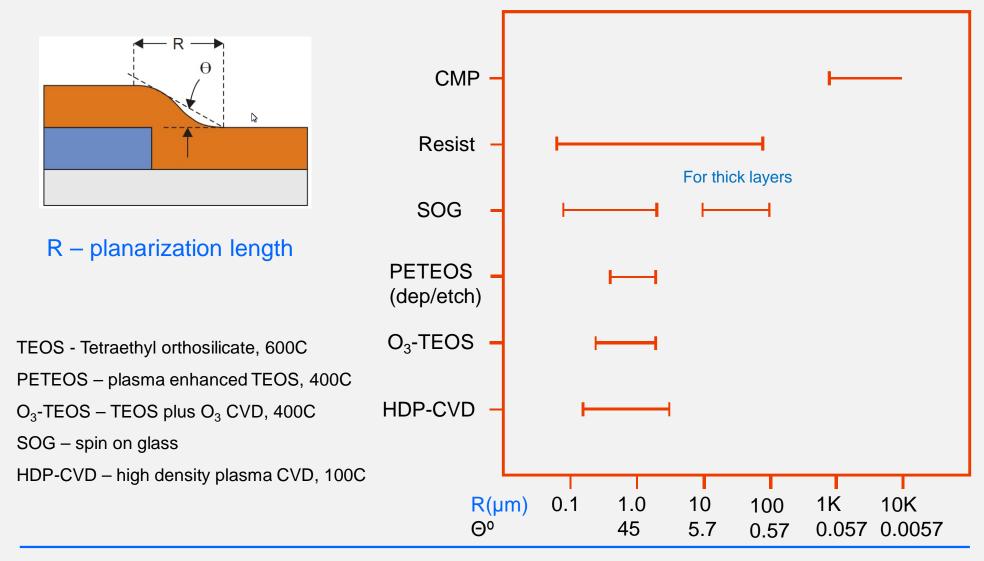

#### **Planarization**

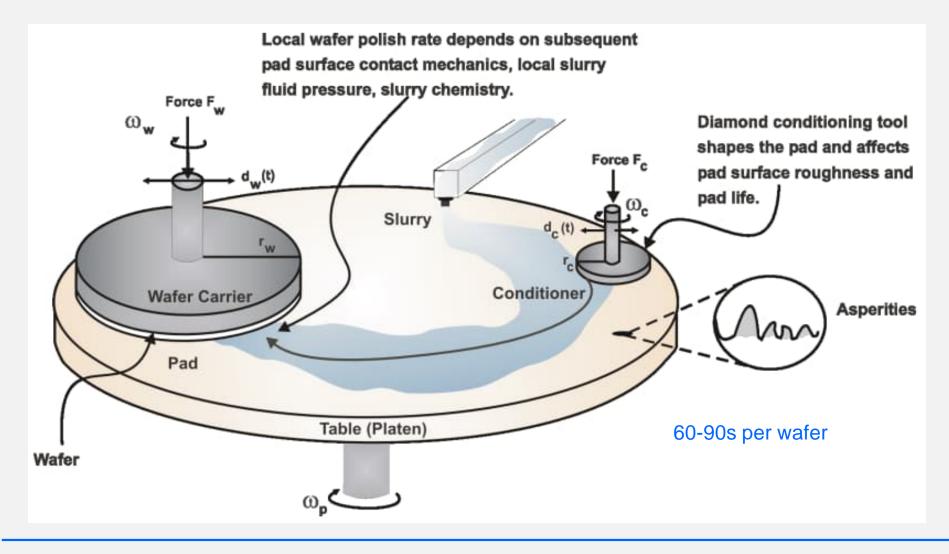

#### Rotary CMP tool

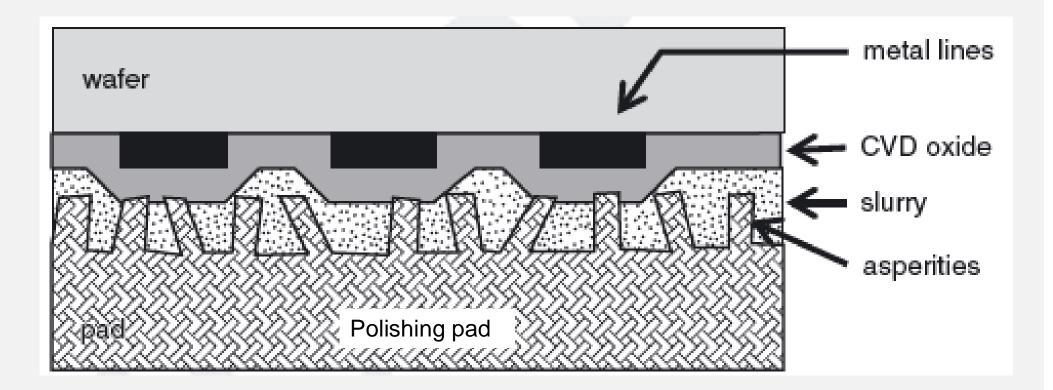

#### Polishing in action

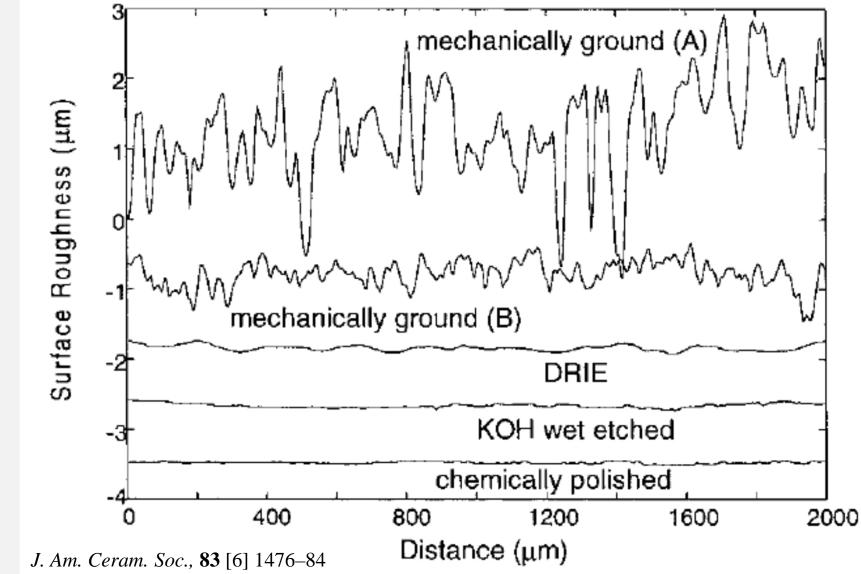

## Grinding vs. polishing

Both use abrasive particles, but:

Grinding removes 10 µm/min in large chunks because large particles Grinding results in very rough surface because very large chunks Grinding leaves mechanical damage due to large chunks being torn off

Polishing uses nanoparticles to achieve smooth surfaces Polishing removes 0.1  $\mu$ m/min because small particles, small forces Mechanism of removal is chemical and mechanical (CMP !) Polishing is needed after grinding !

Surface roughness e.g. 200 nm

Surface roughness e.g. 1 nm

#### Surface roughness

## CMP tool input variables

10-100 rpm

10-100 cm/s

50-500 ml/min

- -platen rotation

- -velocity

- -applied pressure (load) 10-50 kPa

- -slurry supply rate

- -slurry chemicals (pH, conc., viscosity,...)

- -pad (material, porosity, hardness,...)

- -abrasives (size, type, hardness, conc.,...)

- -wafer (curvature, mounting, backpressure)

- -patterns (size, density, ...)

- -films (hardness, µ-structure, stress, ...)

# Process outputs resemble etching ones

- -polish rate, 100-500 nm/min

- -selectivity 1:1 100:1 (blind polishing and stopped polishing)

- -overpolish time

- -pattern density effects

- -uniformity across wafer, 10%

- -wafer-to-wafer repeatability, 10%

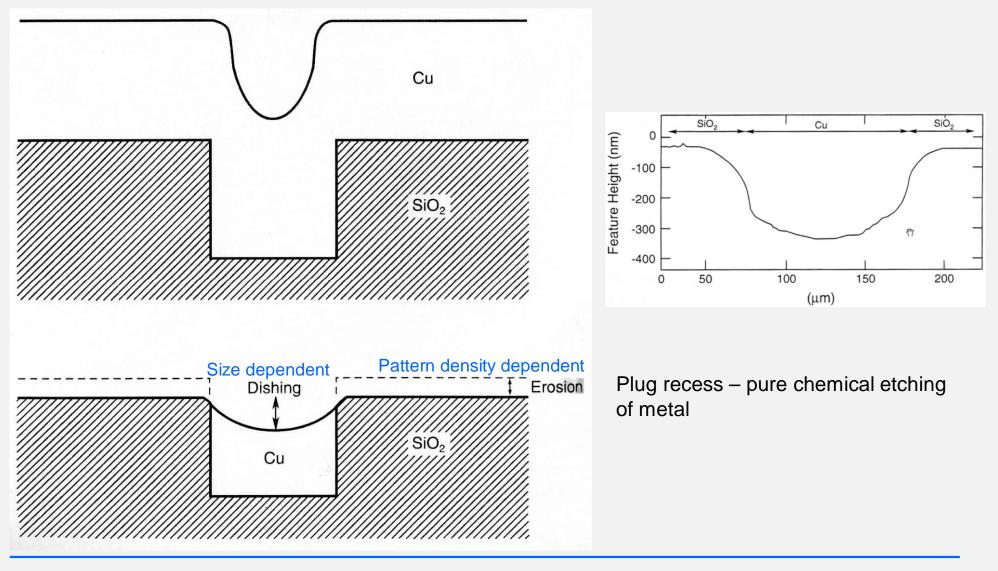

#### Erosion and dishing in CMP

#### A Planarization in multilevel metallization

Silicon VLSI Technology by Plummer et al.

#### **Results of CMP**

#### SiC wafer before and after CMP

- The same rate 100 1000 nm/min

- Surface/transport limitation of reactions

- Pattern dependency is the same, but pattern size effect is opposite

- Chemical and physical effects ions in RIE and mechanical force in CMP

- Preferred directions/planes verticlal in RIE and horizontal in CMP

- Post-CMP cleaning is more chanllenging than post-etching one