Surface MEMS (based on chapter 29) with audioclips

sami.franssila@aalto.fi

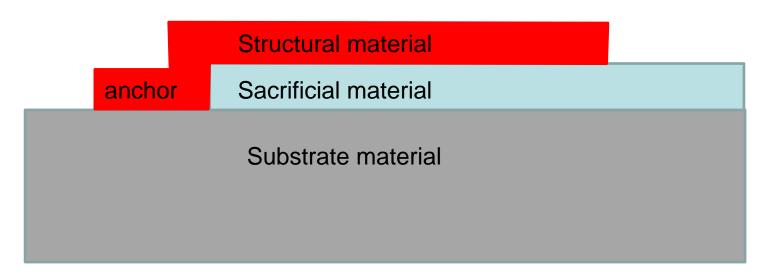

## Generic structure

## Applications

## Isotropic etching

- Proceeds as a spherical wave

- Undercuts structures (proceeds under mask)

- Most wet etching processes are isotropic

- e.g. HF etching of oxide, H<sub>3</sub>PO<sub>4</sub> etching of AI

## Isotropy: good and bad

If you want closely spaced lines (as in comb-drive capacitor), undercutting is bad, but if...

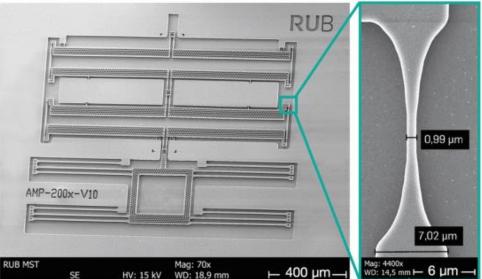

## Single-mask mechanical amplifier

P. Schmitt and M. Hoffmann, "Engineering a Compliant Mechanical Amplifier for MEMS Sensor Applications," in *Journal of Microelectromechanical Systems*, vol. 29, no. 2, pp. 214-227, April 2020.

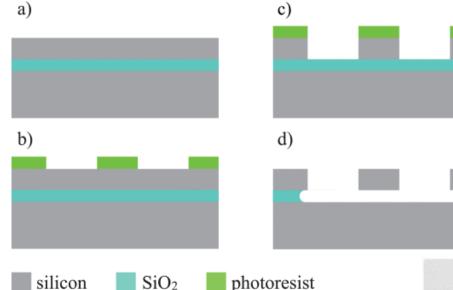

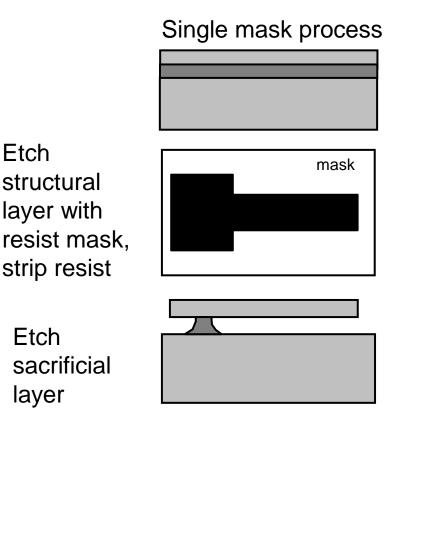

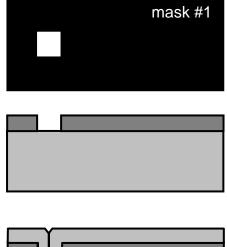

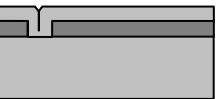

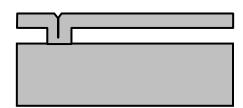

## Single mask vs. two mask cantilever

#### Two mask process

Litho 1 Etch anchor hole in sacrificial layer, strip resist

Deposit structural layer

Litho 2 Etch structural layer, strip resist

Etch sacrificial layer

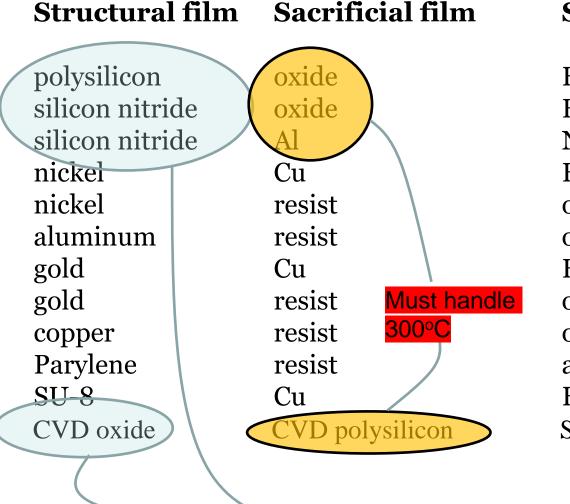

## Material pairs & etchants

Sacrificial etch(es)

HF, HF vapor HF NaOH, H<sub>3</sub>PO<sub>4</sub> HCl oxygen plasma oxygen plasma HCl oxygen plasma oxygen plasma acetone, other solvents HC  $SF_6$  plasma,  $XeF_2$  vapor

Deposition >300°C

## HF etching of SiO<sub>2</sub> and other materials

Thermal oxide

These are CVD oxides

Etchant Material  $SiO_2$  TEOS PSG  $Si_3N_4$  Al Mo 1763 3969 4778 15 HF (49%) 38 0.15BHF 133 107 1024 1 3 0.5 48 1:10 HF 157 922 1.5 320 0.15

#### Etch rates in nm/min

Thermal oxide properties are always the same, but (PE)CVD oxide properties are strongly deposition process dependent

## Polysilicon

- SiH<sub>4</sub> (g) ==> Si (s) + 2 H<sub>2</sub> (g)

- Deposited by CVD at 625°C → true poly

- Can be deposited at 575°C → amorphous

- Typical thickness 100 nm-2 µm

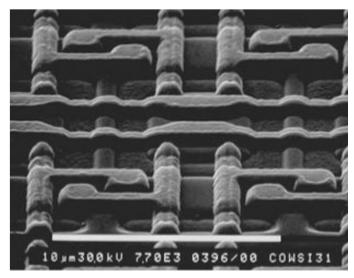

CMOS gate electrodes

**MEMS** rotors

## Poly vs. <Si>

Density: same for both 2.3 g/cm<sup>3</sup> Young's modulus: same for both 170 GPa CTE: same for both 2.5 ppm/K Thermal conductivity: <Si> 156 W/K\*m poly 32 W/K\*m 100 cm<sup>2</sup>/Vs Carrier mobility: <Si>  $10 \text{ cm}^2/\text{Vs}$ poly

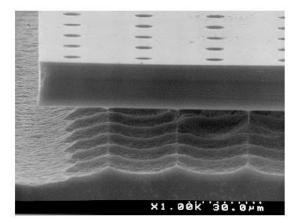

# Compressive stresses in film buckling

Buckling depends on:

- Material (E, υ)

- Bridge span (L)

- Bridge thickness (t)

$$\sigma_{cr} = \frac{\pi^2 E t^2}{3L^2(1-\nu)}$$

Critical buckling stress

#### Desired state of affairs in most cases: structural layer is flat after release

#### This is achieved by (small) tensile stress

## **Tensile stress issues**

Film stays flat.

Defects (e.g. cracks) initiate breakage (aided by high tensile stresses).

## Control of film stress

Marc Madou

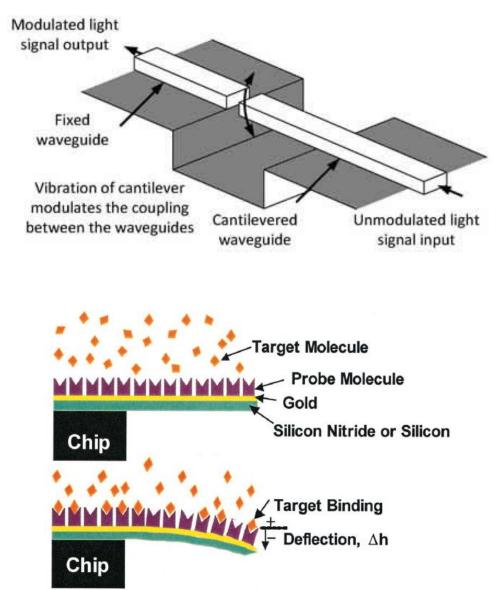

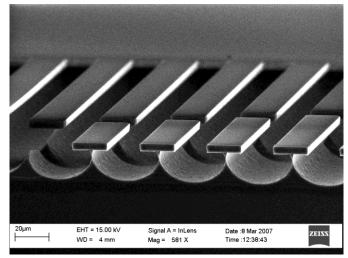

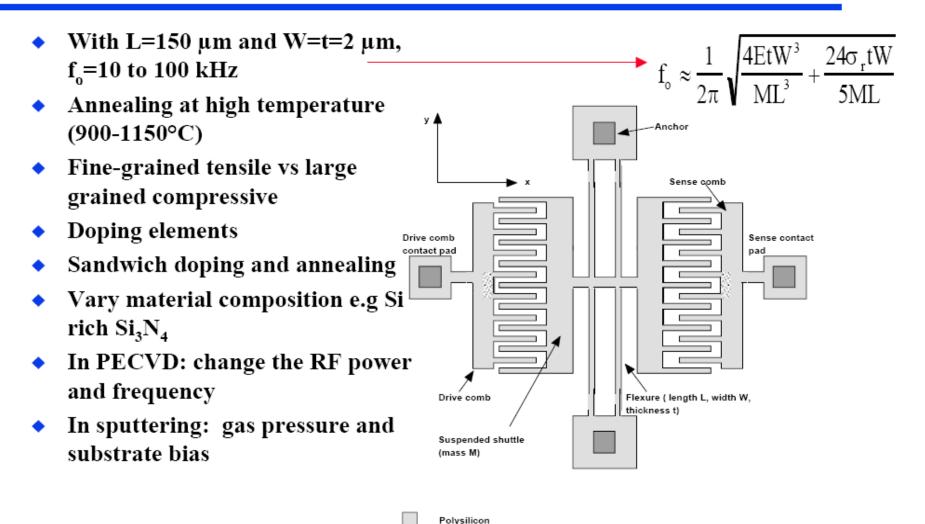

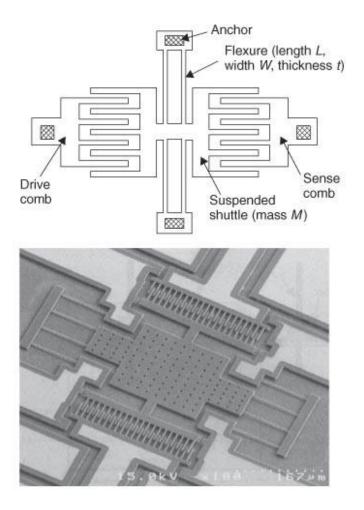

### Perforation to release large area structures

Figure 29-11

Comb drive with suspended shuttle mass. Plate release has been aided by using perforations in the plate. Reproduced from Bustillo *et al.* (1998) by permission of IEEE.

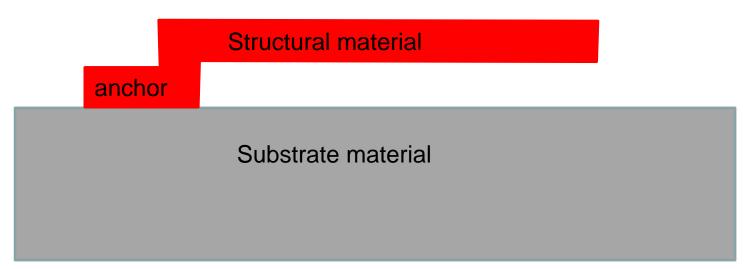

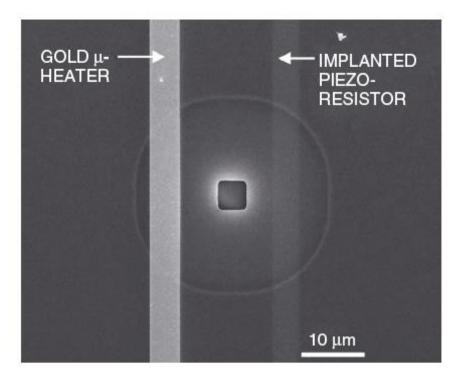

## Thermally excited resonator

Reichenbach, R.B. et al:, IEEE EDL 27 (2006) p. 805

- 1. CVD oxide deposition

- 2. Poly deposition

- 3. Lithography piezoresistor

- 4. Implant piezo & strip

- 5. Clean

- 6. Anneal implant damage

- 7. Au evaporation

- 8. Litho for heater

- 9. Au heater etch & strip

- 10.Litho for poly hole

- 11.Poly etch & strip

- 12.Oxide wet etch in HF

- 13.Rinse & dry

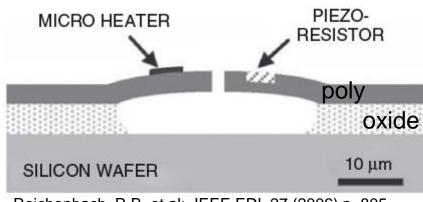

Zuo et al.: CMOS oscillator based on contour-mode MEMS resonators, IEEE 2010

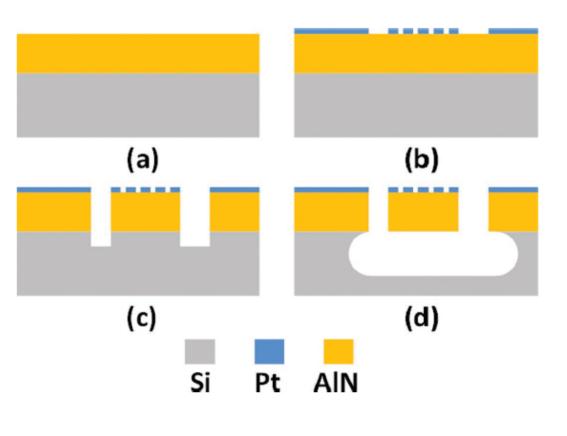

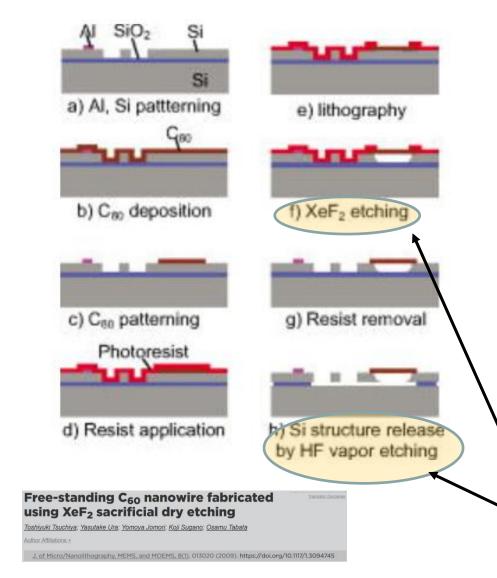

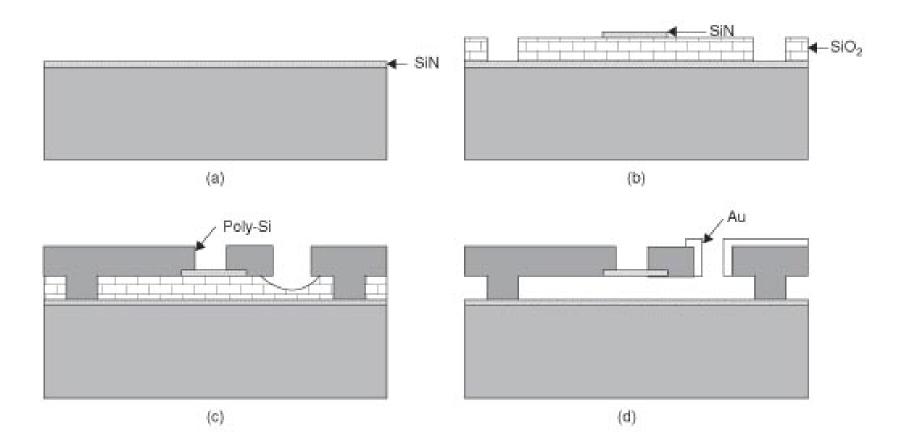

## LFE AIN fabrication

(a) AIN sputter deposition on top of Si wafers (b) lithography, Pt electrode deposition evaporation, lift-off (c) AIN lithography and plasma etching using Cl<sub>2</sub> and BCl<sub>3</sub>, continue to etch into Si (d) structure release by Si dry etching in XeF<sub>2</sub>.

Zuo et al.: CMOS oscillator based on contour-mode MEMS resonators, IEEE 2010

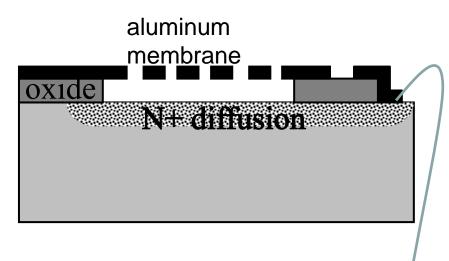

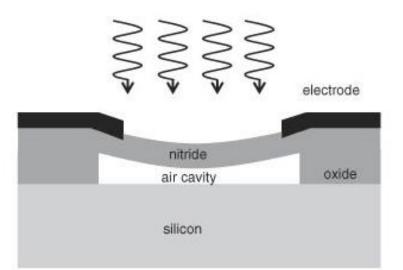

## Microphone

- 0. SSP wafer, low n-doping

- 1. Thermal oxide

- 2. 1st litho for diffusion

- 3. Etch oxide & strip resist

- 4. Clean

- 5. N+ diffusion, heavy doping

- 6. Etch all oxide away

- 7. CVD oxide deposition

- 8. 2nd litho: open contact to n+

- 9. Etch oxide & strip resist

- 10. Aluminum sputtering

- 11. 3rd litho: holes in Al membra

- 12. Etch aluminum & strip resist

- 13. Etch oxide, rinse & dry

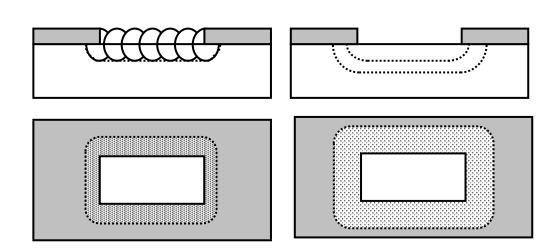

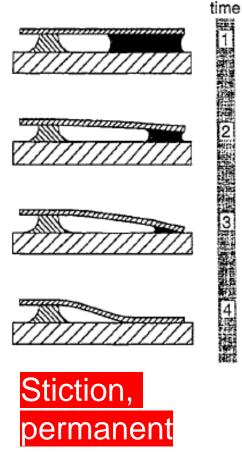

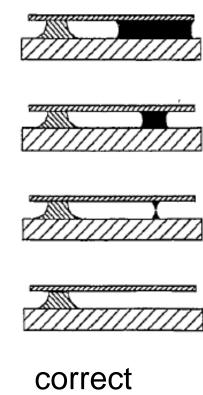

## Stiction ( sticking + friction)

Capillary force of liquid exceeds mechanical strength of the released beam, and the released beam attaches to substrate

release

#### Stiction prevention

- Replace water by something that has lower surface tension, like isopropyl alcohol

- Use stronger structure shapes (H, T, I, U beams)

- Change structural material

- Redesign so that shorter beams needed

- Redesign larger gap (not always possible)

- Make surfaces rough (opposite of good bonding!)

- Use dry release → no drying needed

- Use more elaborate drying (more on next slide)

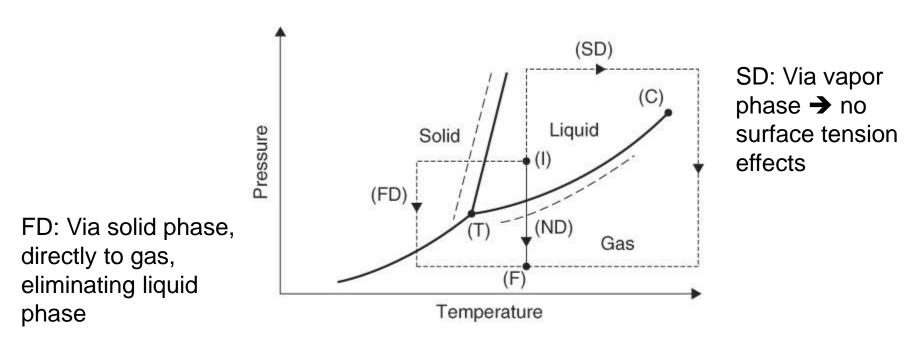

#### Alternative drying

Thermodynamics of drying: I, initial stage; F, final stage; N, normal drying; FD, freeze drying; SD, supercritical drying. Reproduced from Bellet and Canham (1998) by permission of Wiley-VCH.

Introduction to Microfabrication Sami Franssila © 2010 John Wiley & Sons, Ltd

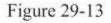

#### Stiction prevention: plasma release

Figure 4. Close-up of the air gap profile near the external edge of the resonator. The holes in the membrane are used to underetch large areas.

No liquid, no surface tension, no capillary forces.

Other plasma releases:

- •SF<sub>6</sub> isotropic plasma etching of silicon

- •NF<sub>3</sub>, CIF<sub>3</sub>, also sources of fluorine to etch silicon

## Dry release, but no plasma

#### XeF<sub>2</sub>:

etches silicon, silicon nitride and molybdenum. Selectivity to oxide >1000:1

#### HF vapor:

etches  $SiO_2$ . Of course, CVD oxides still etch faster than thermal oxide.

Aluminum OK. Nitride selectivity 40-600:1, depends on details.

Two different sacrificial layers !

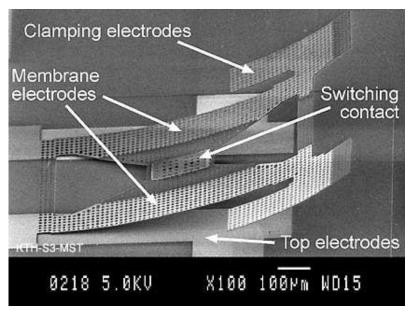

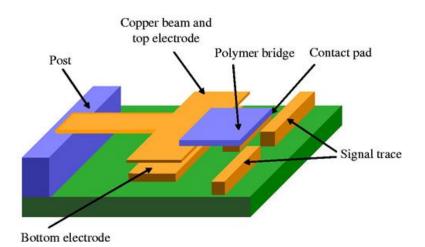

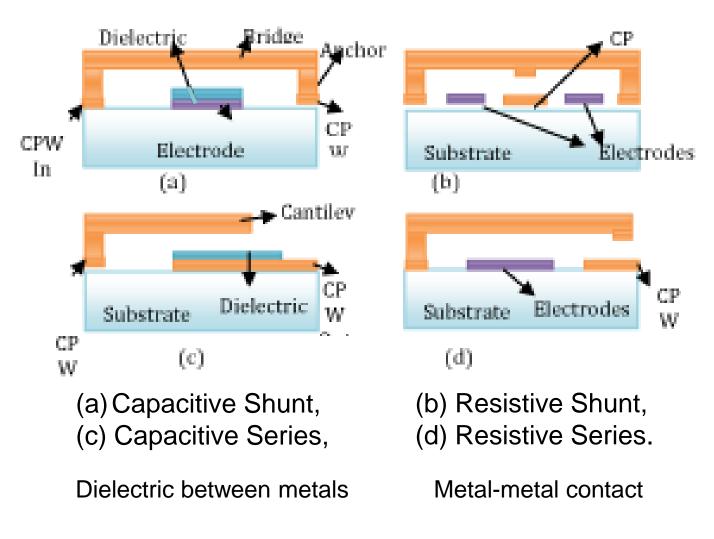

## **MEMS** switches

K. Srinivasa Rao, Lakshmi Narayana Thalluri; Journal of Biosensors, Biomarkers and Diagnostics

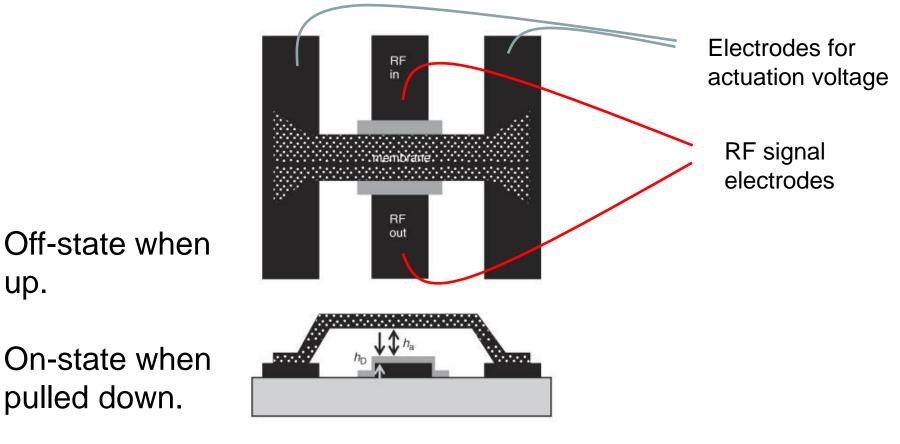

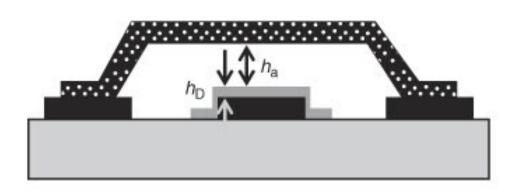

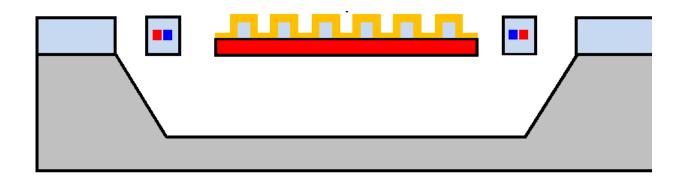

## Capacitive shunt switch

RF switch with nickel membrane, top and cross-sectional views: air gap  $h_a$  created by photoresist sacrificial etching.

Introduction to Microfabrication Sami Franssila © 2010 John Wiley & Sons, Ltd

up.

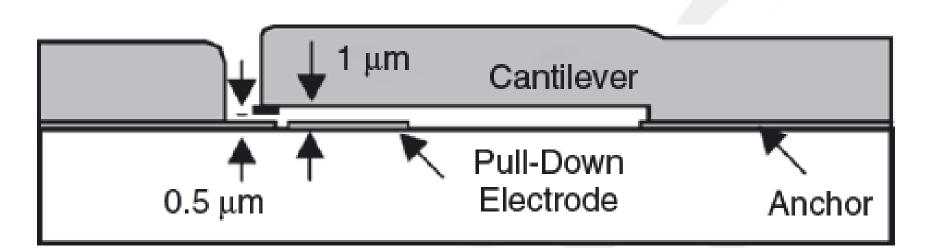

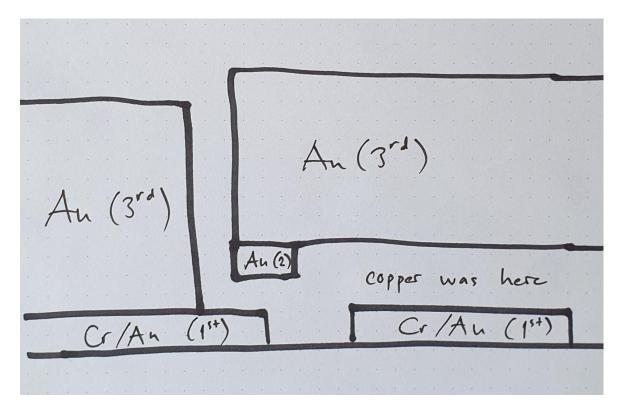

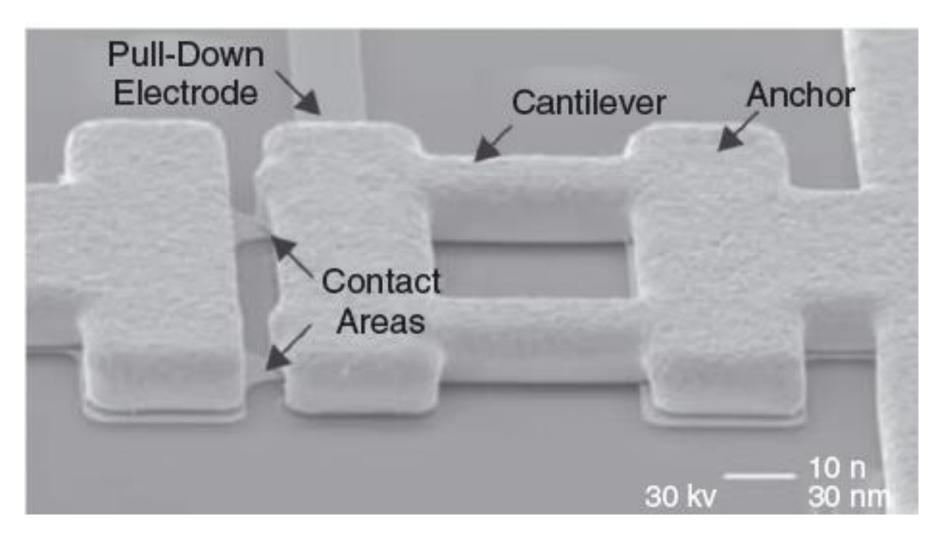

## Electroplated gold switch

Pull down electrode: Cr/Au, 50/250 nm. 1<sup>st</sup> deposition, sputter Sacrificial material: 1 µm Cu Top contact metal: Au, 0.5 µm Cantilever: Au, 8 µm 3<sup>rd</sup> deposition, electroplating

Cr/Au : metal deposition, lithegraphy, etching Sputter Cu/Au, lith. graphy, An wet etching An 0,5 Mm Cu 1 jum Lith + Cu etch Au Cu Lithography + gold electroplating An AL An Ah Au

## Electroplated gold switch

Pull down electrode: Cr/Au, 50/250 nm. 1<sup>st</sup> deposition, sputter Sacrificial material: 1 µm Cu Top contact metal: Au, 0.5 µm Cantilever: Au, 8 µm 3<sup>rd</sup> deposition, electroplating

## Electroplated gold switch

Rebeiz, G.M. & J.B. Muldavin: IEEE Microwave Magazine, Dec. 2001, p. 59

## Critical release gap

## Sometimes gap height is critical for device operation. These gaps are often $\sim 1 \ \mu m$ in size.

Actuation voltage depends on gap height. If gap bad reproducibility → voltage differences in actuation.

Optical path length depends on gap. If gap control bad → no display of colors.

## Non-critical release gap

Gap provides space so that elements can move; or gap provides thermal isolation. Large: >> 1  $\mu$ m

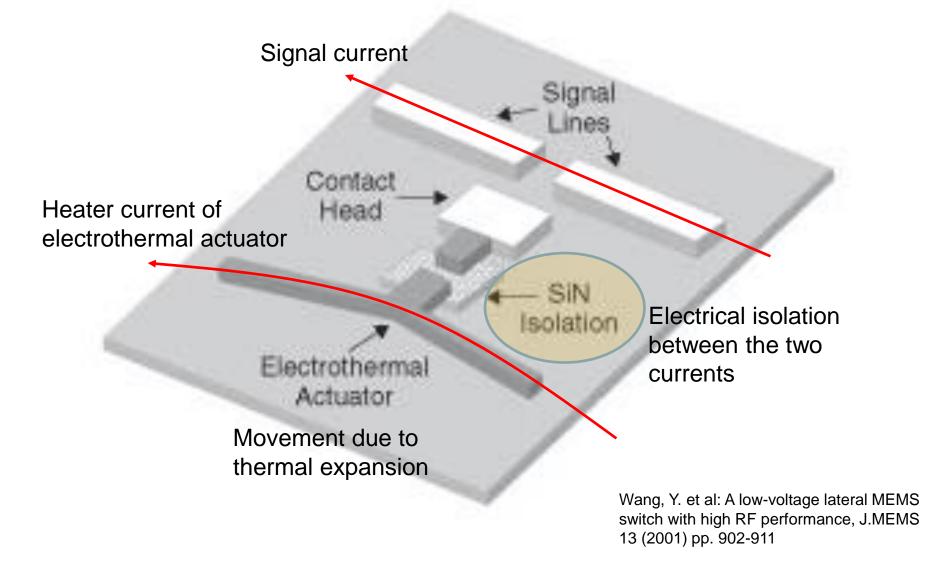

#### Sideways movement thermal relay

## Sideways movement thermal relay

Wang, Y. et al: A low-voltage lateral MEMS switch with high RF performance, J.MEMS 13 (2001) pp. 902-911

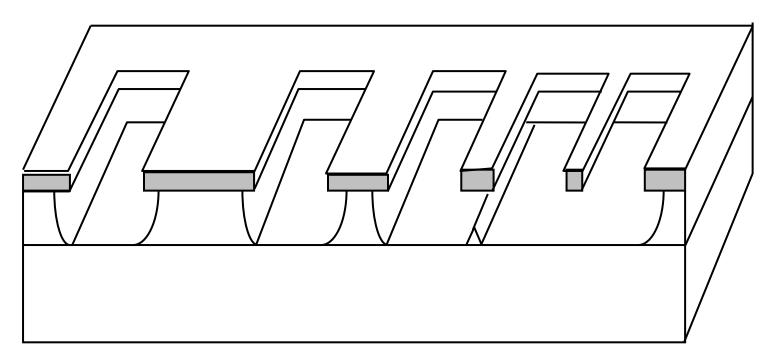

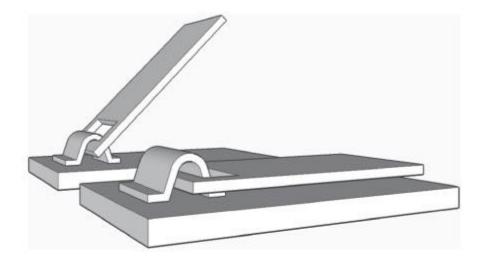

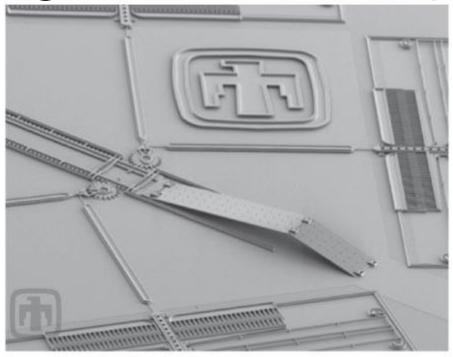

## Hinged structures (1)

Figure 29-22

Two-poly staple hinge. Adapted from Pister et al. (1992) by Jorma Koskinen.

## Hinged structures (2)

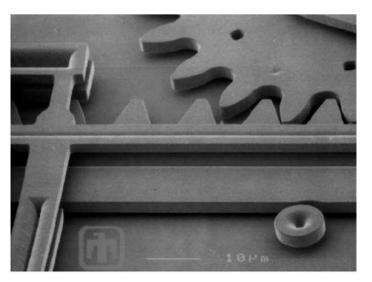

Figure 29-23

Comb-drive actuator-gear system lifts up a hinged mirror. Courtesy Sandia National Laboratories.

Introduction to Microfabrication Sami Franssila © 2010 John Wiley & Sons, Ltd

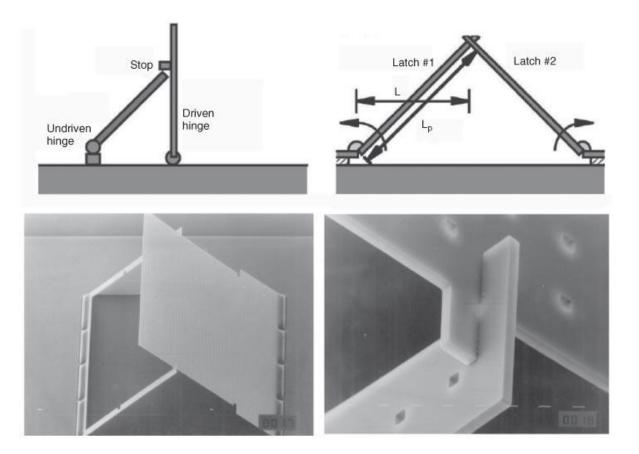

## Hinged structures (3)

Pop-up mirrors with latches. Reproduced from Syms et al. (2001), copyright 2001, by permission of IEEE.

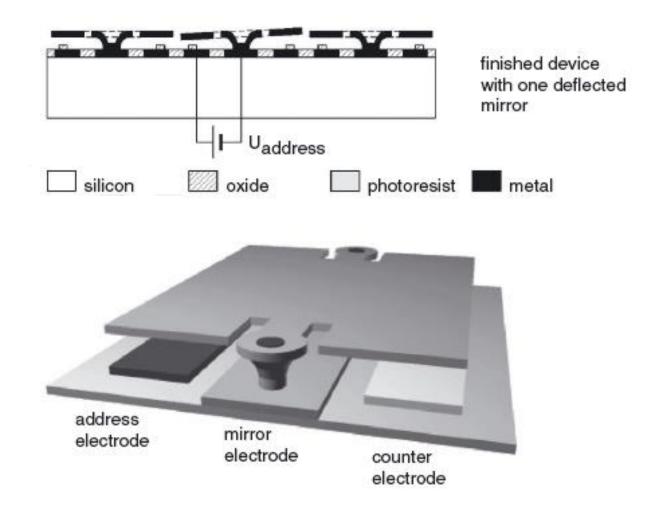

## µ-mirror array on CMOS

Ljungblad, U. et al: New laser pattern generator for DUV using a spatial light modulator, Microel.Eng. 57–58 (2001) pp. 23–29

## Bulk

## SOI

## Surface

<Si> structure heights 380 µm/500 µm (= thru-wafer)

Etched either by KOH or by DRIE.

Hard mask (e.g.  $SiO_2$ ) needed for thru-wafer etching.

Device functionality in SOI device layer

5-50 µm typical device layer thicknesses Device functionality is in thin films (oxide, nitride, poly, aluminium...).

Substrate usually silicon, but can be glass, sapphire,...

Utilizes DRIE to make closely spaced structures like comb-drives.

Aspect ratios e.g. 10:1 or 20:1

Structure heights 1-2 µm (= typical sputter & CVD film thicknesses).

Isotropic sacrificial etching must be used.