# **CIC Decimators and** Interpolators

- An elegant application of multirate digital signal processing is in the design of the oversampling A/D converter

- In this type of converter, the analog signal is sampled at a rate much higher than the Nyquist rate, resulting in very closely sampled samples

Copyright © 2010, S. K. Mitr

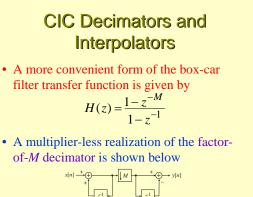

### **CIC Decimators and** Interpolators

- As a consequence, the difference between the amplitudes of two consecutive samples is very small, permitting it to be represented in digital form using very few bits, usually one bit

- The sampling rate is then decreased by passing the digital signal through a factorof-*M* decimator to lower the sampling rate from  $MF_T$  to  $F_T$

Copyright © 2010, S. K. Mitra

Copyright © 2010, S. K. Mitra

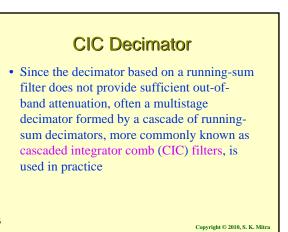

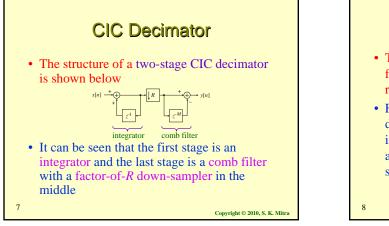

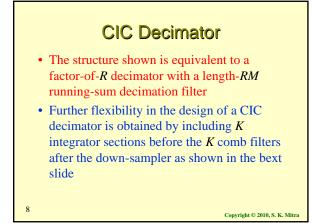

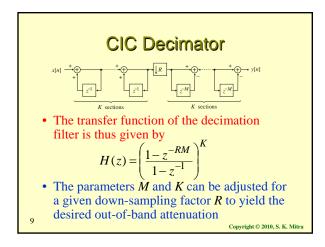

#### **CIC Decimators and** Interpolators • The decimator is designed by cascading an anti-aliasing lowpass *M*-th band digital filter to reduce the bandwidth of the input digital signal to $\pi/M$ with a factor-of-*M* downsampler • The simplest lowpass FIR filter that can be employed is the box-car filter (also called a running-sum filter) with a transfer function $H(z) = 1 + z^{-1} + z^{-1} + \dots + z^{-(M-1)}$

Copyright © 2010, S. K. Mitra

# **CIC Decimators and** Interpolators

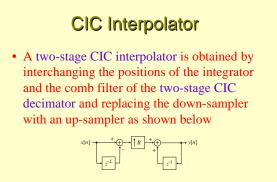

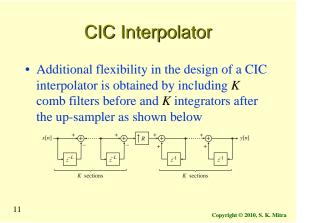

- The recursive running-sum filter can also be employed to design a computationally efficient interpolator

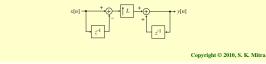

- A multiplier-less factor-of-L interpolator designed using a running-sum filter is shown below

10

- The CIC decimators and interpolators are multiplier-less structures and thus computationally efficient in addition being easy to implement

- However, the wordlength of the adder in each integrator grows rapidly in the multistage implementation

12

Copyright © 2010, S. K. Mitra

Copyright © 2010, S. K. Mitra

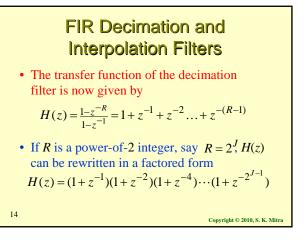

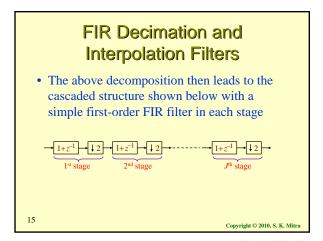

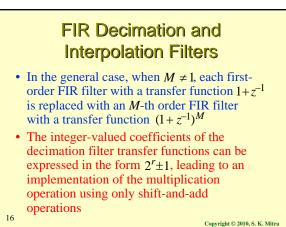

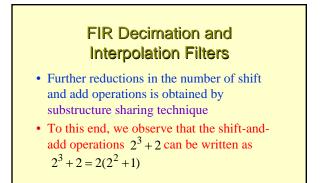

# FIR Decimation and Interpolation Filters

- This problem can be avoided by realizing the running-sum filter in each stage as an FIR filter

- Consider the two-stage decimator shown below for *M* = 1

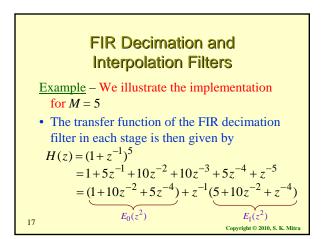

### FIR Decimation and Interpolation Filters

- Thus  $H(z) = E_0(z^2) + z^{-1}E_1(z^2)$

- A schematic representation of a single-stage factor-of-2 decimator based on the above polyphase decomposition is indicated below

18

Copyright © 2010, S. K. Mitra

21

Copyright © 2010, S. K. Mitra

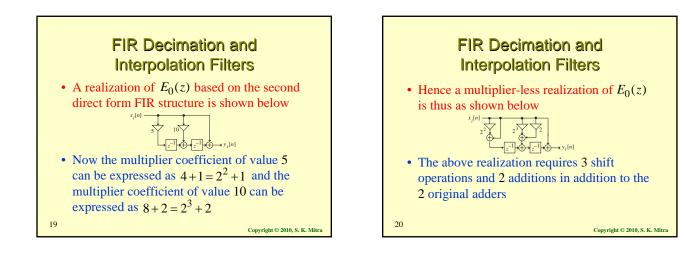

• The shift-and-add operations  $2^2 + 1$  in the expression  $2(2^2 + 1)$  can be shared with the same at the input to the delay chain resulting in the final structure shown below

• The above realization requires 2 shift operations and 3 additions

Copyright © 2010, S. K. Mitra