# **RF IC Amplifiers**

► Focus on specific RF IC amplifiers

LNA and PA

► Some words on buffers

- ► Exercises & Homework

- Self-learning material

- CAD exercise

- Homeworks

# **Basic Small-Signal Amplifiers & Analysis**

#### DC Analysis

- Operating point

- DC current

#### **AC Analysis**

- Gain

- Frequency response

- Input & output impedance

- Stability

# **Basic Small-Signal Amplifiers & Analysis**

#### DC Analysis

- Operating point

- DC current

## **AC Analysis**

- Gain

- Frequency response

- Input & output impedance

- Stability

Main message: RF ICs include conventional amplifier stages and their design resembles that of low frequency basic stages.

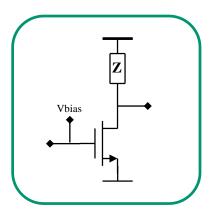

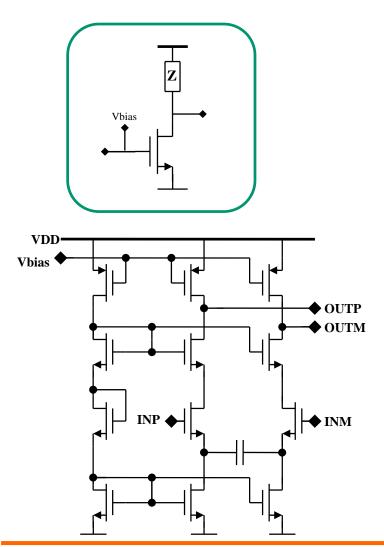

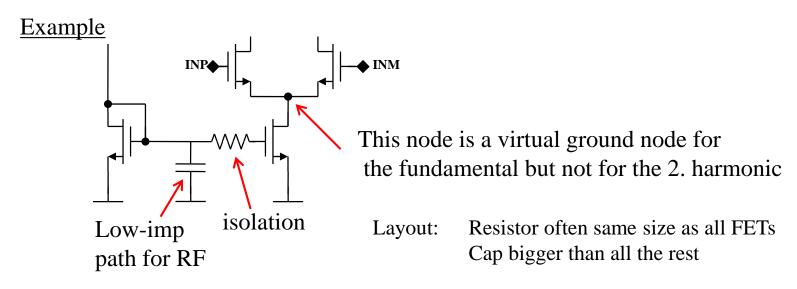

#### **Bias Circuits**

CMOS RF IC circuits have same type of bias arrangments as LF circuits.

#### **Guidelines:**

- 1) Isolate RF signals from bias circuits

- 2) Add low-imp node to bias circuit

- 3) Consider noise coupling, stability, VDD droop etc. just like in LF circuits Interference reduction important; e.g. harmonics of a digital clock

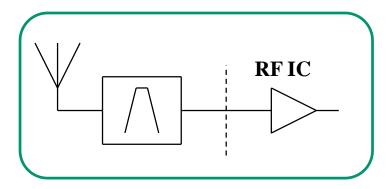

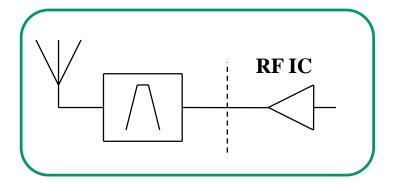

# Impedance Matching "S11" and "S22"

Why do we need input matching for LNA and output matching for PA?

## Impedance Matching "S11" and "S22"

Why do we need input matching for LNA and output matching for PA?

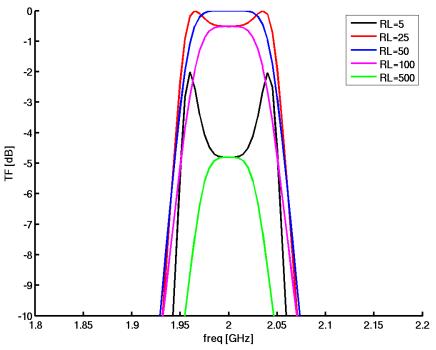

Reason 1:Matching is needed to maintain the correct frequency response of external passive filters.

Reason 2: in LONG interconnections, **signal reflections** results in frequency-depent signal level variations.

## **Low-Noise Amplifier**

#### Four basic circuit arrangements

- Resistive termination

- 2. Parallel feedback

- 3. Common gate

- 4. Inductive degeneration

#### LNA critical design targets

- 1. Gain

- 2. Noise Figure

- 3. Linearity

- 4. Matching

All are frequency dependent !!

Best performance for all these is not met with same dimensioning

→ Compromize is needed

Examples of advanced circuits; "noise cancellation"

# **Basic LNA Configurations**

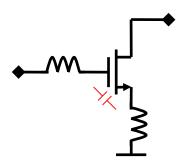

#### **Resistive termination**

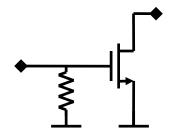

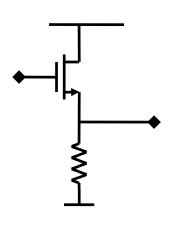

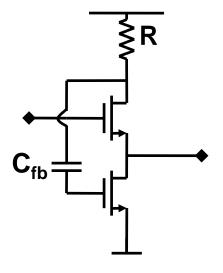

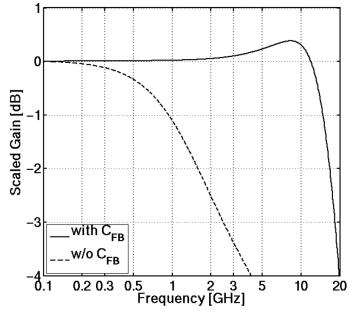

#### Parallel feedback

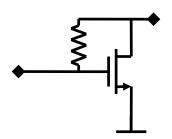

## **Common gate**

## Inductive degeneration

# Input Matching

Resistively terminated

$$Z_{in} = R_m \| Z_{in,T} \|$$

Feed-back

$$Z_{in} = \frac{1}{\sqrt{Z_{in,T} + g_{m,T}}}$$

Common gate

$$Z_{in} = \frac{1}{g_{m,T}}$$

Inductively degenerated

$$Z_{in} = \frac{g_{m,T}L_s}{C_{gs}} + j\left(\omega(L_g + L_s) - \frac{1}{\omega C_{gs}}\right)$$

# Voltage Gain

The voltage gain of the four configurations can be compared by comparing the transconductance  $(G_m = |I_{out}/v_{in}|)$  of each LNA

Resistively terminated

$$G_m = g_m$$

Feed-back

$$G_{m} = \left| \frac{g_{m}R_{fb} - 1}{R_{fb} + Z_{L}} \right| \qquad A_{v} \approx \left| g_{m}R_{fb} - 1 \right|$$

$$A_{v} \approx \left| g_{m} R_{fb} - 1 \right|$$

Common gate (matching req Rin=1/gm≈50)

$$A_{v} = \left| \frac{Z_{L}(j\omega)}{R_{in}} \right|$$

• Inductively degenerated

$$G_m = \frac{1}{\omega_r L_s}$$

(independent of  $g_m$ !)

$$G_m = \left| \frac{g_m}{(j\omega L_g + j\omega L_s - j/\omega C_{gs})j\omega C_{gs} + j\omega L_s g_m} \right|$$

$$G_m = \frac{1}{\omega_r L_s}$$

# **Noise Figure**

Resistively terminated

$$NF = 10\log\left(2 + \frac{\overline{e_{n,out,q}^2}}{kTBR_s(A_v)^2}\right)$$

Feed-back

$$NF = 10\log\left(1 + \frac{R_{s}}{R_{fb}}\left(1 + \frac{R_{fb} + R_{s}}{R_{fb} - R_{s}}\right)^{2} + \frac{\overline{e_{n,out,q}^{2}}}{kTBR_{s}(A_{v})^{2}}\right)$$

Common gate

$$NF = 10\log(1+\gamma) \approx 3...5 dB$$

Inductively degenerated

$$NF = 10\log\left(1 + \frac{e_{n,out,q}^2}{kTBR_s(A_v)^2}\right)$$

# **Linearity - IIP3**

The IIP3 for the memoryless and time-invariant system

$$A_{IIP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \qquad IIP3(dBm) = 10\log \left( \frac{A_{IIP3}^2}{2R_S} \cdot 1000 \right)$$

- For a MOSFET IIP3 related math goes quite complicated

→ we'll rely on simulations

- Traditional study is for BJT collector current

$$I_{c} = I_{S}e^{\frac{V_{BE} + v_{in}}{V_{T}}} = I_{S}e^{\frac{V_{Be}}{V_{T}}} \left[ 1 + \frac{v_{in}}{V_{T}} + \frac{1}{2} \left( \frac{v_{in}}{V_{T}} \right)^{2} + \frac{1}{6} \left( \frac{v_{in}}{V_{T}} \right)^{3} + \dots \right]$$

$$IIP3 = 10\log\left(\frac{4V_T^2}{R_S} \cdot 1000\right)$$

Estimated IIP3 for resistively terminated and common-base BJT LNAs is -13 dBm

## **Comparison of LNA stages**

|           | Resistive termination | Resistive<br>feedback | Common gate | Inductively degenerated |

|-----------|-----------------------|-----------------------|-------------|-------------------------|

| S11       | *                     | *                     | *           | *                       |

| Gain      | *                     |                       |             |                         |

| NF        | <b>6</b> * <b>6</b> * | <b>€</b> **           | <b>6</b> ** | *                       |

| IIP3      |                       | *                     |             | *                       |

| Bandwidth | *                     | *                     | *           | <b>6</b> <sup>¾</sup>   |

Broadband high-linearity LNA (RX) is a BIG challenge!

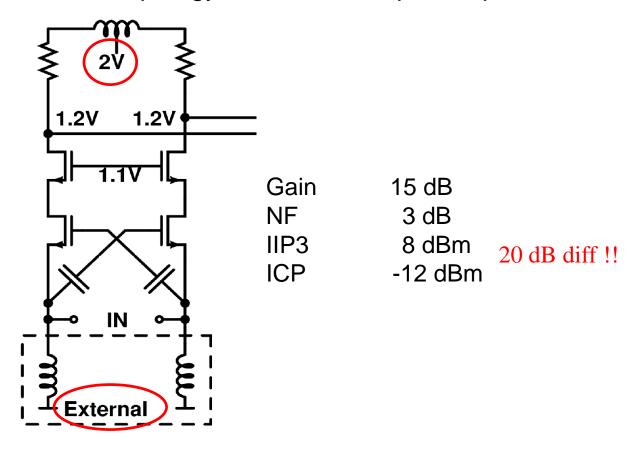

## **Advanced Example I**

CG / CS topology with cross-coupled capacitors

- [1] W. Zhuo et al, "Using capacitive cross-coupling technique ...", ESSCIRC 2000

- [2] W. Zhuo et al, "A Capacitor Cross-Coupled Common-Gate Low-Noise Amplifier", IEEE CAS-II, Dec. 2005

- [3] J. Borremans et al, "A sub-3dB NF voltage-sampling front-end ...", ESSCIRC 2010

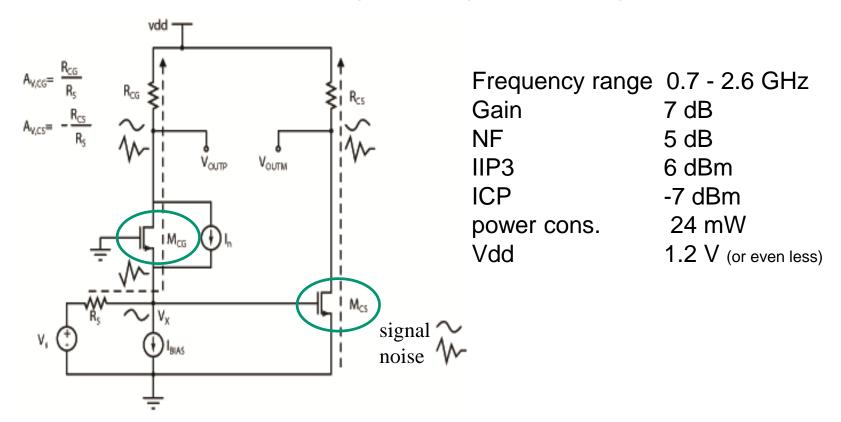

## **Advanced Example II**

CG - CS topology with signal summing

- [1] S. C. Blaakmeer et al, "Wideband balun-LNA ...," IEEE J. Solid-State Circuits, June 2008

- [2] J. Jussila et al, "A 1.2-V highly linear balanced noise-cancelling LNA ...," IEEE J. Solid-State Circuits, March 2008

- [3] K. Stadius et al, "A 0.7 2.6 GHz High-Linearity RF Front-End for Cognitive Radio Spectrum Sensing," ISCAS 2011

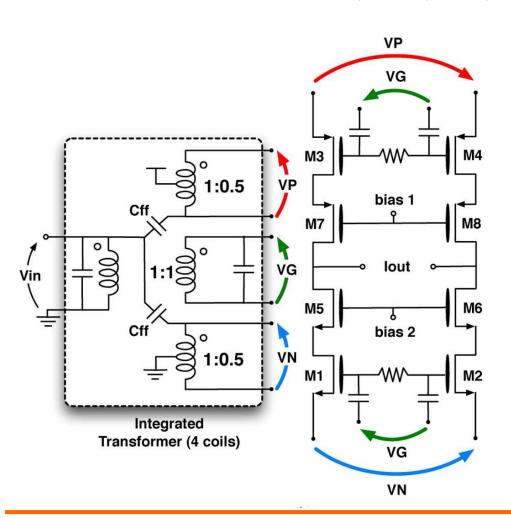

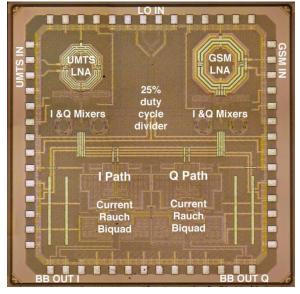

## **Advanced Example III**

I. Fabiano, M. Sosio, A. Liscidini, R. Castello, "SAW-Less Analog Front-End Receivers for TDD and FDD", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 12, DECEMBER 2013

## **Break**

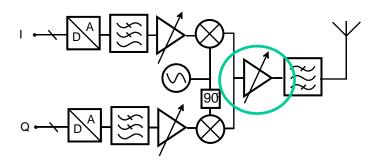

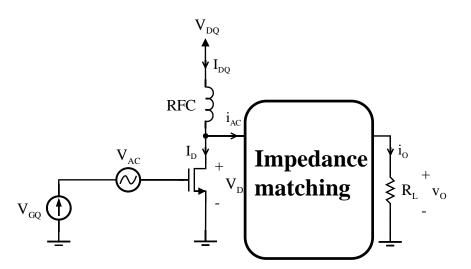

# **Power Amplifiers**

- PA is an amplifier, which has significant output power

- → cannot be treated as a small-signal amplifier

- PA design differs significantly from the other RF IC building blocks:

- Large signal behavior

- thermal effects

- Wiring & transistor size, layout

- Packaging & Interconnections

- breakdown voltages

# Pout ~1 W Pout ~1 W IDC ~ ½ A Pre-power amplifier

## **Topics**

- Figures of Merit

- Classes of Operation (A, B, AB, C, D, E, F, S)

- Comparison on PA classes

Large current

- →large FET

- → large die area

- $\rightarrow$  expensive IC

# **Figures of Merit**

- PA must deliver a sufficient power to the antenna with good efficiency and appropriate linearity.

- Available current through the transistor, supply voltage and load impedance effect on the output power.

$$P_{L} = V_{OUT,RMS} \cdot I_{OUT,RMS}$$

$$R_L = \frac{V_{\text{OUT,RMS}}^2}{P_L}$$

# **Figures of Merit**

- Efficiency

- Describes how effectively the power amplifier transforms the power taken from supply as signal power

- How much of the supply power transforms as unwanted heat

$$\eta = \frac{P_{OUT}}{P_{DC}}$$

# **Figures of Merit**

## Efficiency

- Describes how effectively the power amplifier transforms the power taken from supply as signal power

- How much of the supply power transforms as unwanted heat

$$\eta = \frac{P_{OUT}}{P_{DC}}$$

- Efficiency does not take into account the input signal

- Power added efficiency (PAE) does take it into account

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}} = \frac{P_{OUT}}{P_{DC}} \left( 1 - \frac{1}{G} \right) = \eta \left( 1 - \frac{1}{G} \right)$$

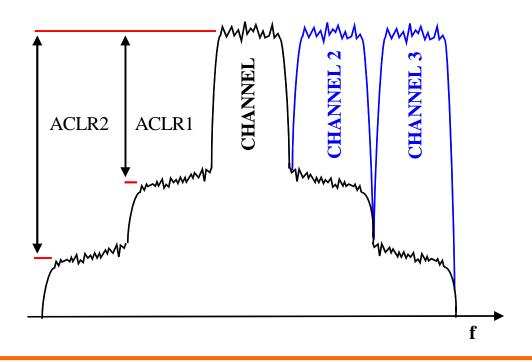

## **Linearity Requirements**

- Use a modulated signal as input signal and examine its behavior at PA output.

- Signal spreading is characterized with adjacent channel leakage ratio (ACLR).

# **Power Amplifier Classes**

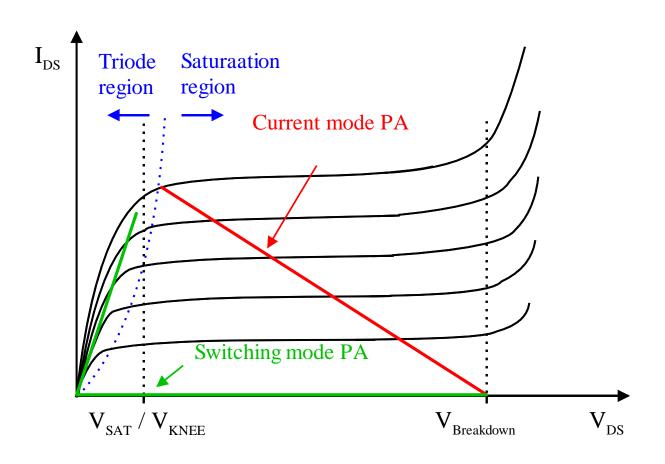

Current mode "Linear PA"

Switching mode "Non-linear PA"

Class A

Class **B**

Class C

Class **D**

Class E

Class **F**

Class S

"Ordinary" amplifier, Idrain off only for a while

Transistor is a switch Idrain on-off Output network modifies signals

# **Operation Principles**

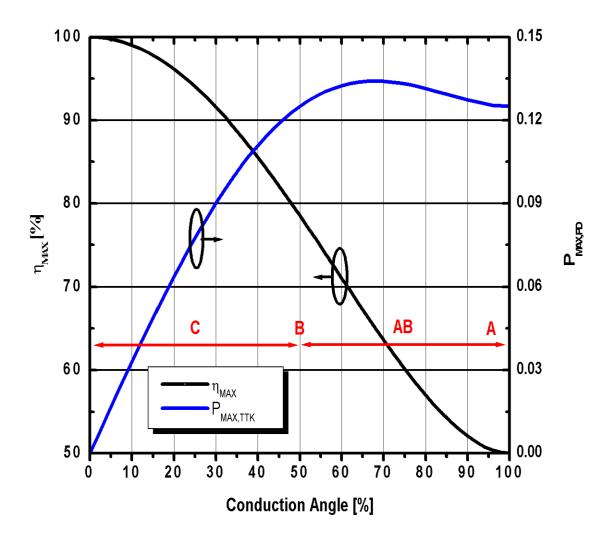

# Linear PA (class A, B, C)

Class A: conduction angle 100% (I<sub>DD</sub> flows all the time)

Class B: conduction angle 50% Class C: conduction angle → 0%

## **Linear PAs**

#### Class A

- Conduction angle 100%

- 50% efficiency is reached at maximum output power

- Rapid degradation in lower powers

- Consumes significant power without input signal

#### Class B

- Conduction angle 50% → lower DC power

- maximum efficiency 78,5%

- Slower degradation in lower powers

- Gain 2-6 dB lower compared to class A

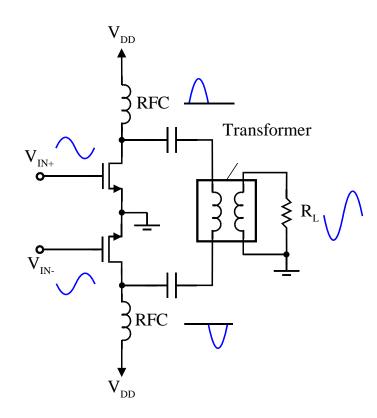

# Class B push-pull

- Linearity of class B PA can be improved by using a push-pull topology

- Each PA branch must produce only half of the output power →relaxes the design of output matching network

- Optimum output load resistance of each branch is double

- Requires additional inductors

#### Class C

- Conduction angle 0% 50% → low DC power

- In ideal case PA has a negative biasing point → reverse breakdown voltage requirement

- Nonlinear

- Class C PA is most suitable for phase modulation systems.

- Class C PA can be designed using similar equations as class A and B PAs.

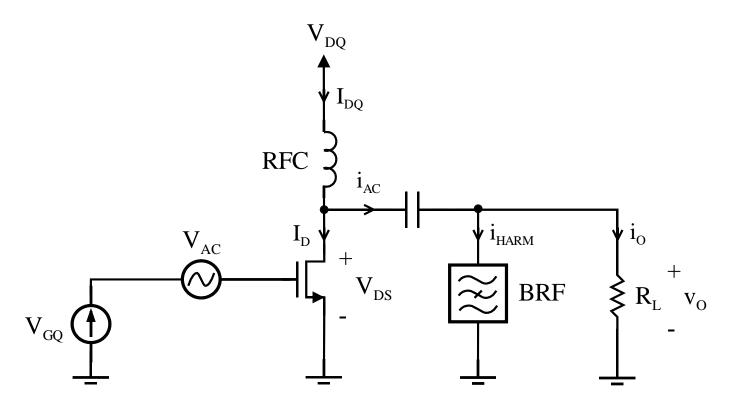

#### **Nonlinear PAs**

- Class D, E, F, and S power amplifiers

- In high efficiency PAs the design principle is to minimize the voltage-current product over the transistor.

- The losses degrading efficiency arise from transistor nonidealities (internal capacitors, resistors, finite rise and fall times) and from losses in matching networks and losses to substrate.

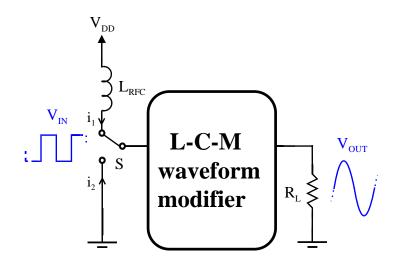

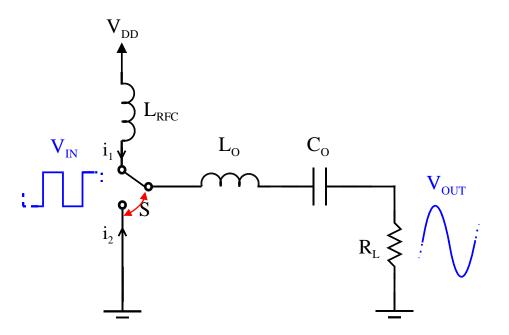

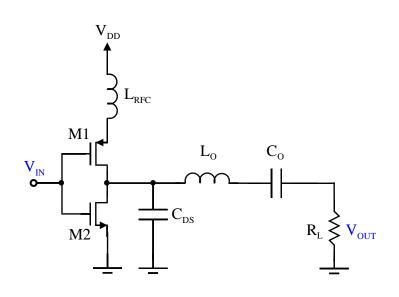

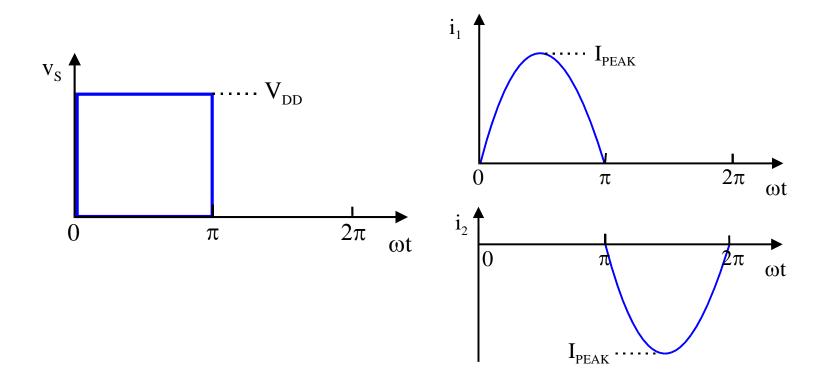

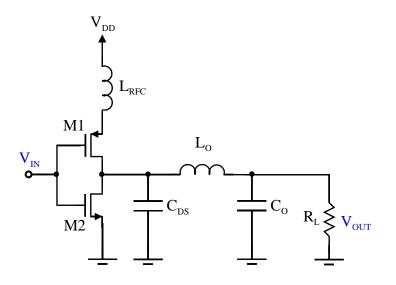

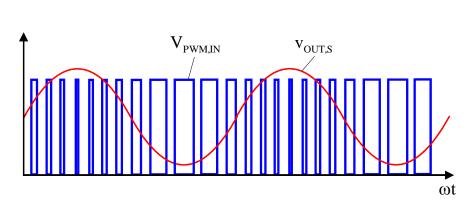

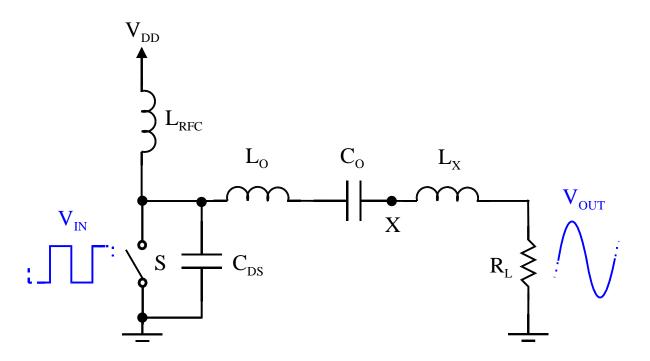

## Class D

PA includes switch S, series resonator (L<sub>o</sub>, C<sub>o</sub>, and R<sub>L</sub>) and biasing inductor L<sub>RFC</sub>.

#### Class D

• PA includes switch S, series resonator ( $L_o$ ,  $C_o$ , and  $R_L$ ) and biasing inductor  $L_{RFC}$ .

#### Class S

- Class S PA is identical to class D PA when comparing its analysis and design equations.

- Difference in these PAs is in the topology.

- Applications of class S PA can be typically found from audio frequency amplifies.

#### Class E

Operation principle of the class E PA is to minimize the losses caused by the nonidealities of switch.

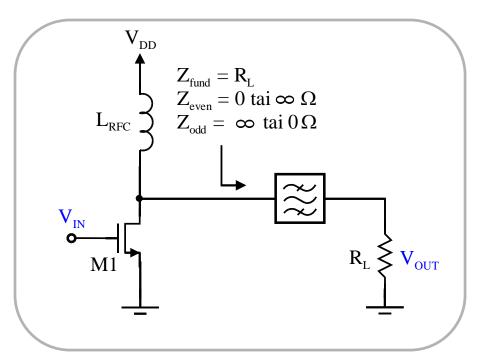

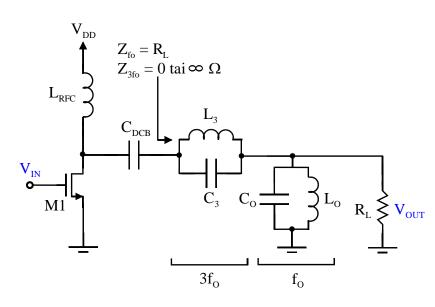

#### Class F

- In class F PA the efficiency is increased by using harmonic resonators to modify the output current and voltage waveforms

- Adding harmonics to transistor current and voltage waveforms the transistor waveform begins to approach the ideal switch waveform

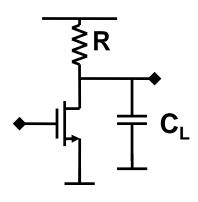

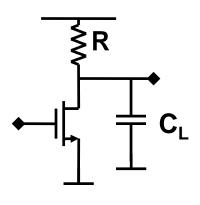

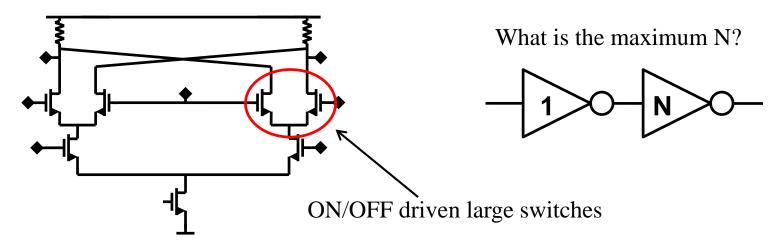

## **Buffers**

How to drive large devices i.e. low-impedance nodes?

- High gain = large R, but  $C_L$  in parallel  $\rightarrow$  low gain

- Driving capability  $\sim \frac{I_{bias}}{\omega C_L V_{sig}}$

## **Buffers**

How to drive large devices i.e. low-impedance nodes?

- High gain = large R, but  $C_L$  in parallel  $\rightarrow$  low gain

- Driving capability  $\sim \frac{I_{bias}}{\omega C_L V_{sig}}$

## **Examples**

## **Buffers**

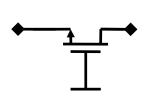

## **Source follower**

## Super source-follower

voltage gain ≈ 1

$$R_{out} \sim \frac{1}{g_m} + caps$$

BTW, you can almost always replace resistor R with a FET i.e. active load or current source.

# **Self-Learning Assignment 3**

Objectives are to familiarize yourself with

- typical RF IC LNA design issues

- doctoral dissertation on the RF IC field

You can find the assignment from

MyCourses / Assignments - SLA / Self-learning assignment 3

Return your answer as a pdf-file to Return Box in the same page

# **Next Meeting Tuesday 19.4.**

#### Topics will be

- concepts related to mixers

- active mixers

- passive mixers

- examples