Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences**

Integrated RF circuits Spring 2023

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

## **RF IC Technologies and Devices**

Brief review on RF IC technologies

- MOS technology

- Passive devices

- Bonding

- Self-learning assignment 2

#### Exercises & Homework

- CAD exercise

- Homeworks

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **RF IC Technologies**

#### Gallium Arsenide

- MESFET

- HEMT

- HBT

GaAs technologies have no or poor p-type FETs  $\rightarrow$  no complementary devices  $\rightarrow$  no good digital logic

#### Silicon / SiGe

- BJT

- BiCMOS

- CMOS

Technologies for very high speed or power

- InP

- GaN

- SiC

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

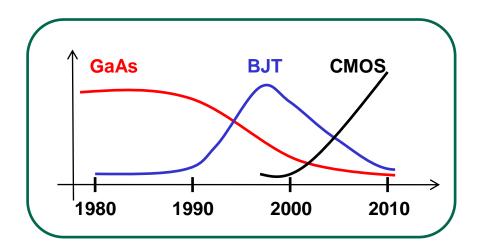

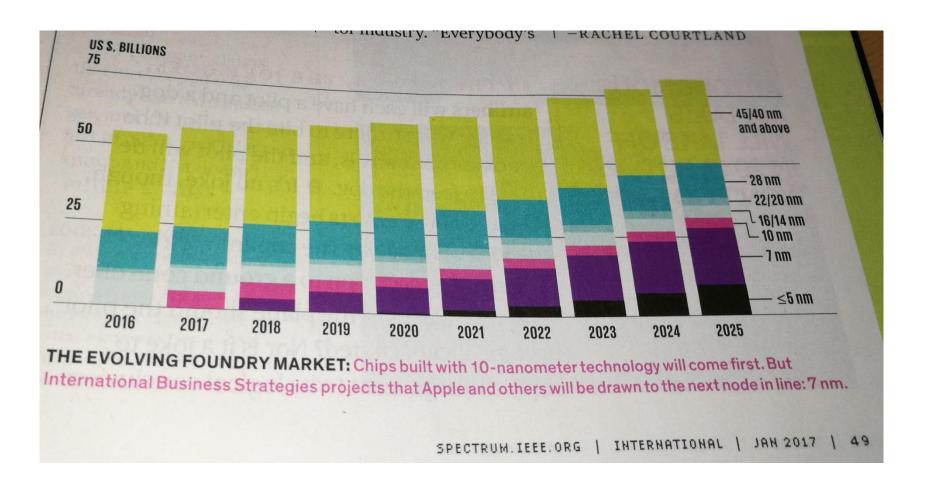

## **RF IC designing has and will change ...**

#### Trends:

- Technology

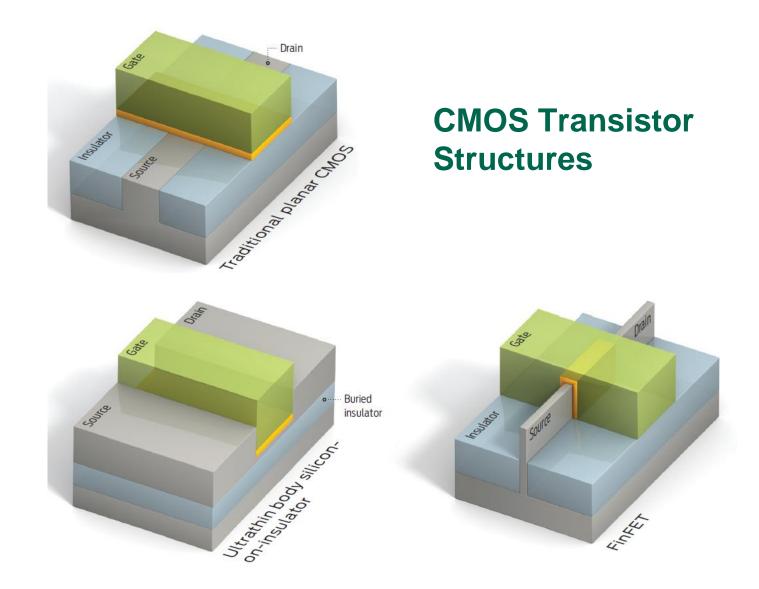

- GaAs → Si BJT → BiCMOS → bulk CMOS → FD-SOI & Finfet CMOS

- Design complexity

- Circuit  $\rightarrow$  Block  $\rightarrow$  RX-TX-SX  $\rightarrow$  multi-system, SOC, SDR

- Design paradigm:

- RF engineering  $\rightarrow$  RF IC design  $\rightarrow$  Multi-mode design

- Designers

- Spesialists  $\rightarrow$  in-house groups  $\rightarrow$  fabless & foundry groups

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

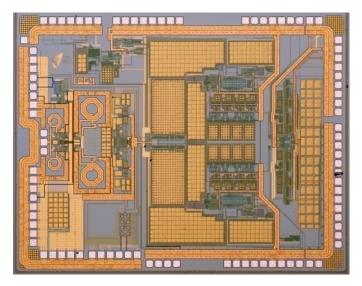

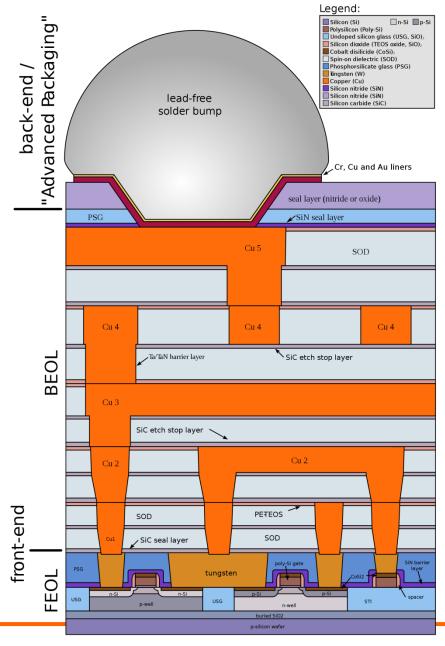

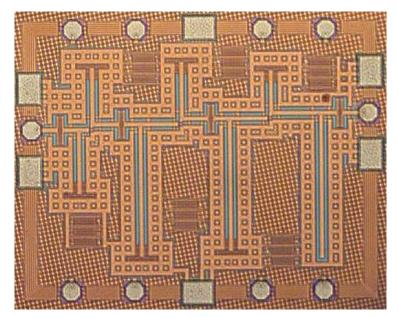

# **Typical RF CMOS Process**

- Gate lenght: 65 nm  $\rightarrow$  40 nm  $\rightarrow$  **28 nm**  $\rightarrow$  14 nm  $\rightarrow$  10 nm  $\rightarrow$  7...5 ... 3 nm

- Typical device  $f_t$  100-300 GHz

- 6-10 metal layers (copper or aluminium)

- NMOS & PMOS devices

- 2-3 threshold voltage ( $V_T$ ) levels

- Specific RF devices = RF model & layout

- Core devices simpler (model & layout)

- Passive devices <u>with</u> RF model

- Inductors and transformers

- Capacitors (MIM)

- Varactors (MOS & pn)

- Resistors (poly-silicon, 2-3 different R<sub>sq</sub>)

- Digital cell libraries (VHDL  $\rightarrow$  compiler)

Modern CMOS technology is very versatile and good for RF ICs. Critical practical challenge is the quality (and availability) of device **MODELS.**

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

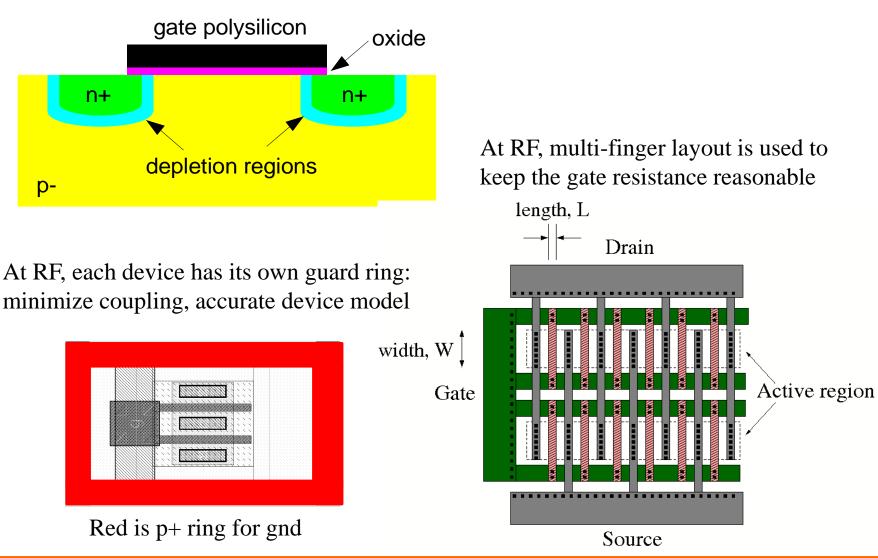

# **NMOS Device**

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# CMOS Cross-Section

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences**

Integrated RF circuits Spring 2023

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

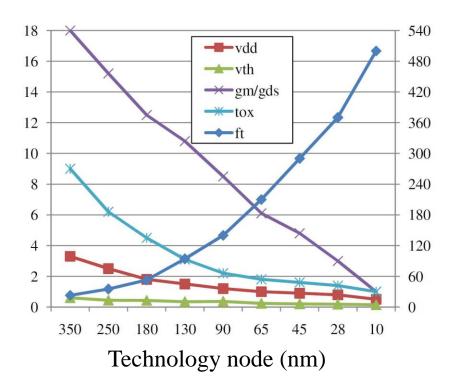

# **CMOS Scaling: Analog performance is declining**

CMOS evolution has resulted in

- increased integration density

- higher speed

- low supply voltage  $\rightarrow$  low power

- reduced signal headroom

- declined analog performance

- Intrinsic gain gm/gds declines

- Output impedance is low

- = good switch, poor amplifier

#### Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

### Moore's law has hold well

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

Aalto University School of Electrical Engineering

Ahmed, K.; Schuegraf, K.; "Transistor wars," IEEE Spectrum, vol. 48, no.11, pp.50-66, Nov 2011

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **FD-SOI and FinFET Technologies**

#### A video on FD-SOI by ST Microelectronics

https://www.youtube.com/watch?v=uvV7jcpQ7UY

#### A video on FinFET by ThresholdSystems

https://www.youtube.com/watch?v=c-3p8moNXfI&t=0s

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

## **Passive Devices in RF CMOS process**

- 1. Resistor

- 2. Inductor

- 3. Transmission line

- 4. Capacitor

- 5. MOS varactor

- 6. SC network

- 7. Bonding pad

- 8. Wire bonding

- 9. Flip-chip (BGA)

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **Quality Factor Q**

Quality factor Q is a metric to describe the losses of reactive component BUT, it is also used in filter design to define the steepness of your filter  $\rightarrow$  A risk to a confusion.

- Q=10, low-quality passive such as on-chip coil

- Q=100, already close to ideal in most cases

- Q>1000, losses play role only in special cases

## **Quality Factor Q**

The most general definition of the Q-factor is based on the ratio of stored energy to dissipated energy per cycle:

$$Q = \frac{E_{store}}{E_{diss} / \omega}$$

For an ideal inductor with a series resistor R, we have

$$Q = \omega \frac{\frac{1}{2}Li^2}{\frac{1}{2}Ri^2} = \frac{\omega L}{R}$$

Alternative definition is based on 3-dB bandwidth of a resonator / filter

$$Q_{3dB} = \frac{\omega_0}{\Delta \omega_{3dB}}$$

Now, consider an ideal (lossless) LC-bandpass filter: Q is infinite,  $Q_{3dB}$  is real.

Department of Micro and Nanosciences Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

Aalto University School of Electrical Engineering

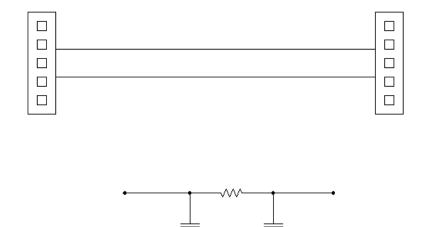

# **Integrated Resistor**

- Sheet resistance typ. 100-300  $\Omega$

- Quite small parasitic capacitance, OK for RF ICs

- Process variation significant, typ. 20-50 %

- "well"-type silicon resistors not good for RF; High Cpar

Department of Micro and Nanosciences Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

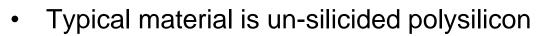

#### **Monolithic Inductor**

Very important for RF ICs  $\rightarrow$  Self-learning assignment

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

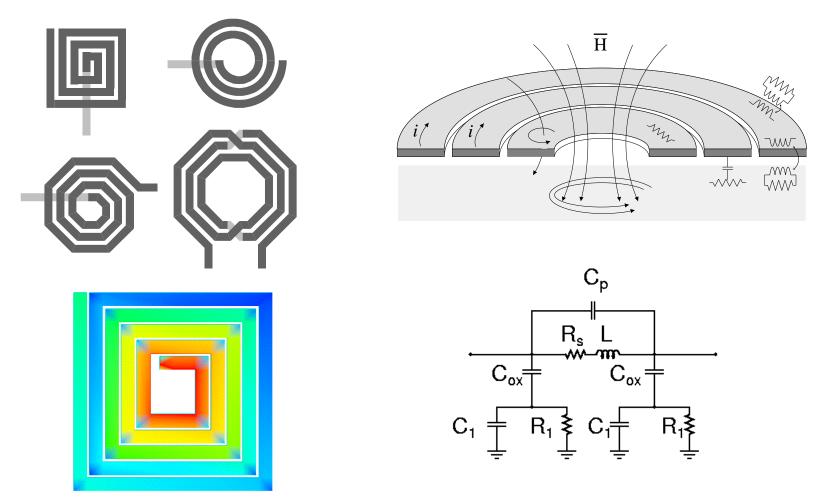

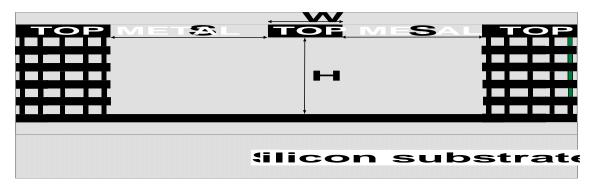

#### **Integrated Transmission Line**

Microstrip line  $h \ll s$

# Coplanar waveguide (CPW)

| TOPMETS          | L TOP MESAL | TOP |

|------------------|-------------|-----|

|                  |             |     |

|                  |             |     |

|                  |             |     |

| i ni mi mi mi mi |             |     |

|                  |             |     |

|                  |             |     |

|                  |             |     |

|                  |             |     |

| ilicon substrate |             |     |

|                  |             |     |

|                  |             |     |

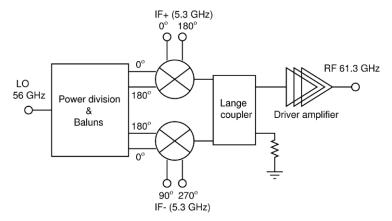

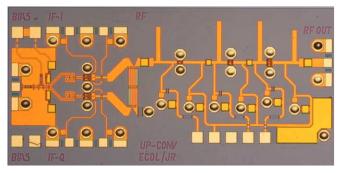

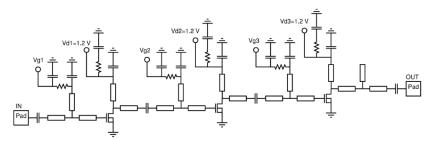

## **Examples of Transmission Line Circuits**

@ Jan Riska

A 60-GHz three stage amplifier

@ Mikko Varonen

**Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

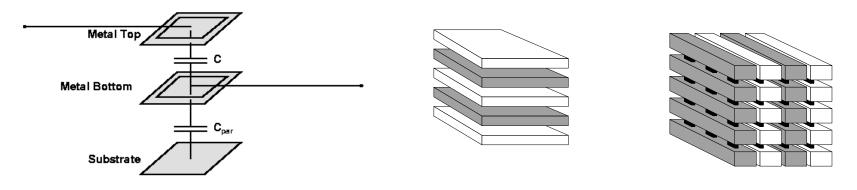

# **Integrated Capacitors**

Metal-insulator-metal (MIM)

Sandwich MIM

Lateral flux

- Main issues are capacitance density and C/Cpar

- Quality factors are high; take care of interconnections

- In sub-100nm technologies lateral flux caps are better

- Process variation significant, typ. 10-30 %

Department of Micro and Nanosciences Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

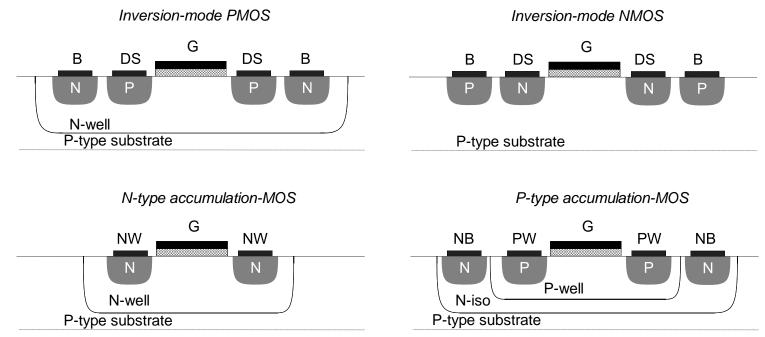

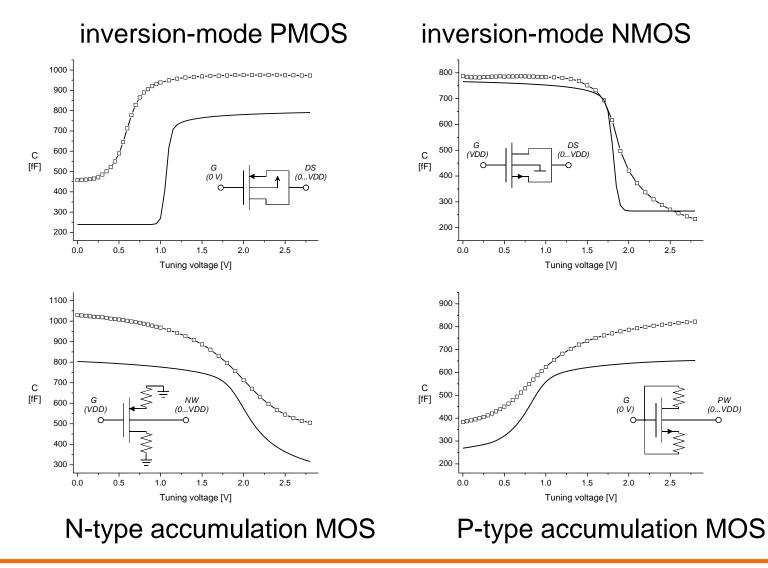

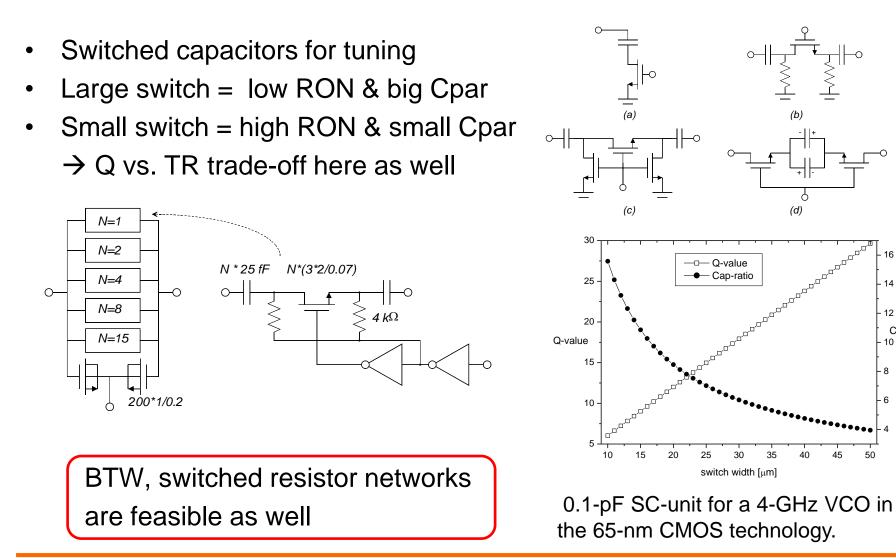

## **MOS varactors**

- Four types are available, inversion-mode are "ordinary" MOSFETs

- Quality factor and tuning range (Cmax/Cmin) are competing properties

- Typ. Q~50 at 2 GHz and Cmax/Cmin ~3

- Process variation tracks to MOSFET variation

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

#### **MOS Varactors**

Aalto University School of Electrical Engineering

#### **Department of Micro and Nanosciences**

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **Switched-Capacitor Network**

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

alto University School of Electrical Engineering

Integrated RF circuits Spring 2023

16

14

12

10

8

50

C/Coff

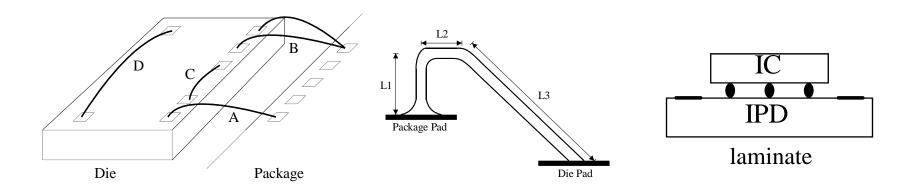

# Wire Bonding and Flip-Chip Assembly

- Bond wire = high-Q inductor, L=1nH / mm, typ. 1-3 mm

- Ball-grid array solder bumb H=100-200 um, Ø~50 um small high-Q inductor

- Flip-chip requires substrate (laminate) and second bonding → modeling !

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

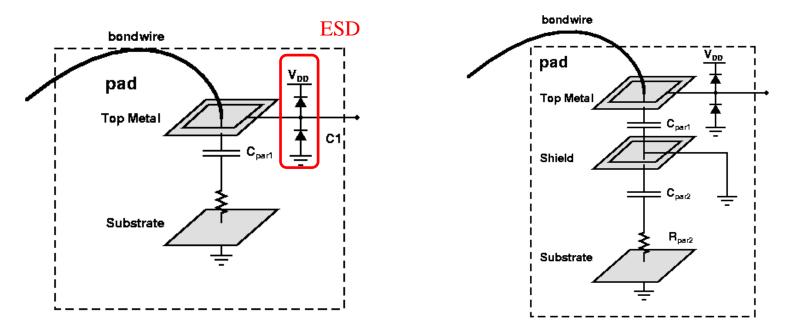

# **Bonding Pad**

- Pad produces parasitic capacitance

- ESD protection circuit produces a large parasitic capacitance

- "RF pad" model needed in a design kit

Department of Micro and Nanosciences Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

## Recap

**RFIC** technologies

- CMOS is the prevalent tech best for mixed mode apps

- SiGe BiCMOS for mmWave applications

- GaN for power amplifiers

- InP for very high frequencies

**RFIC** components

- Model availability / accuracy is the key question

- Coils are a specialty of RF ICs

- Transmission lines appear at above 50 GHz

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **Next Meeting**

Topics will be

- concepts related to amplifiers

- low-noise amplifiers

- power amplifiers

- buffers

Aalto University School of Electrical Engineering

**Department of Micro and Nanosciences** Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

# **Self-Learning Assignment 2**

Objectives are to familiarize yourself with properties of **monolithic coils** and transformers

Department of Micro and Nanosciences

Integrated RF circuits Spring 2023

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi

## **Session continues at 14:15**

Introduction & guidance on homeworks and CAD exercises.

Department of Micro and Nanosciences

Kari Stadius, Saeed Naghavi, Kimi Jokiniemi