4

# Electrical Ratings and Characteristics of Power Semiconductor Switching Devices

Device characteristics and ratings are primarily concerned with electrical and thermal properties. The thermal properties and cooling design aspects are similar for all power switching semiconductor devices. A common, unified thermal design approach is applicable since manufacturers use the concept of a semiconductor device being thermally represented by one *virtual junction*. This virtual junction is considered as the point source of all losses, which comprise on-state and off-state losses as well as switch-on and switch-off losses and any control input loss.

Not only are the power dissipation characteristics similar for all semiconductor devices, but many similarities exist in the area of maximum device ratings.

#### 4.1 General maximum ratings of power semiconductor devices

The maximum allowable limits of current, applied voltage, and power dissipation are defined as the *maximum ratings* for that device. These absolute maximum ratings are important and the device must not experience a condition under which any one limit is exceeded if long life and reliability are to be attained. Generally, at worst, the device should experience only one near maximum rating at any instant.

Ratings are dependent on the materials used, the structure, the design, the mount, and the type of processes employed. The one property inherent in these physical features is temperature dependence and its interaction on electrical properties. Maximum ratings are therefore generally based on the variation of

Power Electronics 69

electrical characteristics that arises from the created variations. Because of this close correlation between properties, different ratings cannot be considered independently. Also, ratings are highly dependent on the device external circuit conditions.

This interdependence of device properties and the effects of external circuit condition are no more evident than during thermal runaway - a condition to be avoided. Such a condition can occur in all devices that have bipolar junctions. For example, with the diode, thyristor, and the MOSFET's parasitic diode, reverse recovery current increases junction temperature. The reverse recovery charge increases with temperature, thus increasing junction power dissipation and further raising the junction temperature. This endless increasing of temperature and recovery charge results in thermal runaway and eventual device destruction. A similar thermal runaway condition occurs in the bipolar transistor and devices employing BJT mechanisms, like the thyristor and the IGBT. Here, collector current causes an increase in temperature which increases the conductivity of the bipolar transistor. More current then flows, further increasing the device temperature. If external circuit conditions allow, thermal runaway occurs, thus resulting in irreversible device damage.

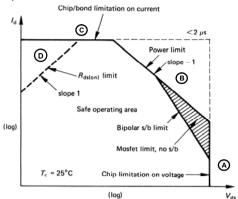

Figure 4.1 shows the electrical operating bounds of common semiconductor power switches, where the general trend is the higher the *I-V* ratings the slower the possible switching frequency, (because of increased losses associated with attaining higher sustaining voltages), hence increased junction temperature. High-frequency low-power switching applications are dominated by the MOSFET or possibly trench-gate IGBTs while high-power low-frequency switching applications are dominated by thyristor type devices or possibly IGBT modules. Rectifying or fast recovery diodes, as appropriate, are available with matched *I-V* ratings for all the switch device types in figure 4.1.

#### 4.1.1 Voltage ratings

The absolute voltage limit is characterised by a sharp increase in leakage current when the device has at least one junction reverse-biased. The most commonly experienced voltage-limiting mechanism is that of avalanche multiplication, as considered in chapters 2.2.2 and 3.1.2. Since leakage current increases significantly with increased temperature, as shown in figure 2.2 and given by equation (2.7), the absolute repetitive voltage rating must be assigned such that thermal runaway does not occur. Most voltage ratings, because of historic reasons, are characterised at an impractical case temperature of 25°C. The leakage current at rated voltage and 25°C varies from hundreds of microamperes for low voltage devices (less than 600V) to milliamperes for high voltage devices (>3.3kV).

Figure 4.1. Electrical rating bounds for power switching silicon devices, where (a) frequency related losses limit upper power through-put and (b) voltage is restricted by silicon limitations while current is bounded by packaging and die size constraints.

Power Electronics 71

#### 4.1.2 Forward current ratings

The forward current ratings are usually specified after consideration of the following factors.

- Current at which the junction temperature does not exceed a rated value.

- Current at which internal leads and contacts are not evaporated.

- External connector current-handling capabilities.

#### 4.1.3 Temperature ratings

The maximum allowable junction temperature  $T_{j,\max}$ , is dependent on the quality of the materials used and the type of junction, and is traded off against the reduced reliability that arises from deterioration and accelerated service life. The higher the junction temperature, the higher the rate of deterioration. The relationship between service life  $L_i$  in hours, and the junction temperature  $T_i$  (K) is approximated by

$$\log_{10} L_i \approx A + B/T_i \tag{4.1}$$

where A and B are constants which are related to the device type.

### 4.1.4 Power ratings

Power dissipated in a semiconductor device is converted into thermal energy which produces a temperature rise. The major parameters limiting the maximum allowable power dissipation  $P_{t, \max}$  are the maximum allowable junction temperature and the device case temperature  $T_c$ . These parameters are related to one another by the thermal resistance  $R_a$  according to

$$P_{d \max} = \frac{T_{j \max} - T_c}{R_{g_{jc}}} \tag{W}$$

The virtual junction to case thermal resistance  $R_{\theta_{j-c}}$  is a physical value representing the ratio, junction temperature rise per unit power dissipation. Thermal resistance is a measure of the difficulty in removing heat from the junction to the case. Most maximum power values are specified at a case temperature of 25°C, and are derated linearly to zero as the case-operating temperature increases to  $T_{jmax}$ , which is typically 175°C for silicon power switching devices.

## 4.2 The fast-recovery diode

Static *I-V* diode characteristics were considered in chapter 2 and chapter 3.1. In low-frequency applications the only problem posed by a rectifier is heat dissipation, which can be readily calculated if the current waveform is known. On the other hand, calculation of losses in rectifiers for high-frequency application requires knowledge of device switching phenomena. The forward and reverse recovery characteristics are the most important fast-recovery bipolar pn diode electrical switching properties.

#### 4.2.1 Turn-on characteristics

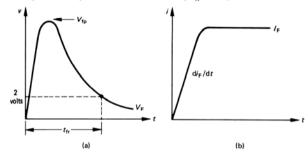

During the forward turn-on period of a rectifier, an overshoot voltage is impressed in a forward bias direction across the diode as the forward current increases. The forward recovery characteristics of time  $t_{fr}$  and peak forward voltage  $V_{fp}$  are measured as shown in figure 4.2, with a specified increase in forward current  $di_{F}/dt$ , rising to a maximum forward current level  $I_{Fr}$ .

Two mechanisms predominate and contribute to the voltage overshoot phenomenon. The first mechanism is resistive, while the second is inductive.

Initially at turn-on, the device resistance is dominated by the ohmic resistance of the low-concentration n-region. As the concentration of the injected minority carriers increases, the n-region becomes conductively modulated and the associated ohmic drop decreases significantly. These charging effects contribute to a minor initial capacitive component which serves to clamp  $V_{\ell p}$  initially to zero.

Figure 4.2. Diode forward recovery measurement: (a) specification of forward recovery time,  $t_n$  and peak forward voltage,  $V_n$  and (b) diode anode current test waveform.

Figure 4.3. Diode forward turn-on characteristics for two initial anode di/dt cases: (a) forward current and effective change in resistive component, r and (b) anode voltage and voltage contribution  $v_i$ , as a result of die inductance.

The forward  $di_F/dt$  causes a voltage drop across the internal device inductance. This inductance comprises both the diode wafer inductance and the bonding and connection inductance. In bipolar power devices, the inductance of the wafer predominates. Any inductance contribution to the forward transient voltage ceases when the steady-state current level  $I_F$  is reached, as shown in figure 4.3. It will be seen that the peak forward transient voltage increases as  $di_F/dt$  increases. The resistive component predominates at low  $di_F/dt$ .

As with most minority carrier based power semiconductor characteristics, the turn-on phenomenon is significantly worsened by an increase in junction temperature. That is, both  $t_{fr}$  and  $V_{fp}$  are increased with temperature. Although a pre-reversed biased junction condition does not significantly prejudice the turn-on characteristics, if the junction is pre-forward biased slightly, the turn-on transitional phase can be significantly reduced. The Schottky diode, a majority carrier device, does not suffer from forward turn-on transient effects.

#### 4.2.2 Turn-off characteristics

When a forward-conducting bipolar junction diode is abruptly reverse-biased, a short time elapses before the device actually regains its reverse blocking capabilities. Most importantly, before the diode does regain blocking ability, it may be considered as a short circuit in its normally blocking direction.

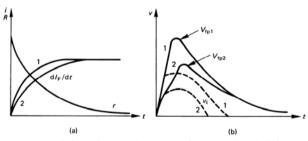

During forward conduction there is an excess of minority carriers in each diode region and the holes in the n-region and electrons in the p-region must be removed at turn-off. The attempted reverse bias results in a reverse current flow as shown in figure 4.4.

The total recovery charge  $Q_0$  is given by

$$Q_0 = \tau I_{\scriptscriptstyle E} \tag{4.3}$$

where  $I_F$  is the forward current before switching. In the usual p<sup>+</sup>n diode, the excess minority holes in the n-region are most dominant. The lifetime  $\tau$  is therefore the hole lifetime  $\tau_h$ . Since carrier lifetime increases with temperature, recovery charge increases with temperature.

The recovery charge  $Q_0$  has two components, one due to internal excess charge natural recombination and the other, the *reverse recovery charge*  $Q_R$ , due to the reverse diode current shown in figure 4.4.

The excess charges reside in the neutral scl regions of the diode that border the junction. The excess charge concentration is largest at the scl edge on the n-side, reducing to zero well before the cathode contact.

Turn-off is initiated at  $t_f$  and the reverse recovery current  $i_{rr}$  commences. The rate of rise of this current is determined solely by the external inductance L of the switching circuit and the circuit applied reverse voltage E, according to

$$\frac{dI_F}{dt} = -E/L \qquad (A/s) \tag{4.4}$$

Until the time  $t_0$  the diode carries forward current and is forward-biased. When the current reverses, the forward voltage drop decreases slightly but the device still

remains positively biased. The external circuit inductance L supports the voltage E. The excess carrier concentrations now begin to reduce as holes leave via the junction, in providing the reverse current,  $i_{rr}$ . Holes are therefore extracted first and quickest at the edge of the scl.

Figure 4.4. Diode voltage and current during reverse recovery at turn-off.

At time  $t_I$ , the hole concentration at the scl edge reaches zero, the charge  $Q_I$  has been removed and charge  $Q_2$  remains. The reverse current now reduces rapidly since insufficient holes exist at the scl edge. The scl widens quickly, as it is charged. That is, the diode regains its ability to support reverse voltage and at the maximum reverse current  $I_{RM}$ ,  $dI_{P}/dI$  reduces to zero.

Since  $dI_F/dt = 0$ , the voltage across the circuit inductance L drops rapidly to zero and E is applied in reverse bias across the diode. Between  $t_1$  and  $t_2$  the rate of change of reverse current  $di_{rr}/dt$  is high and, in conjunction with L, produces a reverse voltage overshoot to  $V_{RM}$ . After time  $t_2$ ,  $di_{rr}/dt$  reduces to zero, the circuit inductance supports zero volts, and the diode blocks E.

In specifying the reverse recovery time,  $t_{rr} = t_2 - t_0$ , the time  $t_2$  is defined by projecting  $i_{rr}$  through  $\frac{1}{4}I_{RM}$  as shown in figure 4.4. The reverse recovery time  $t_{rr}$  and peak reverse recovery current  $I_{RM0}$  at high magnitude  $dI_rIdt$  such that  $Q_R \approx Q_0$ , are approximated by

$$\begin{split} t_{rr} &\approx 2.8 \times 10^6 \ V_b \sqrt{I_F / |dI_F / dt|} & \text{(s)} \\ \text{and} & I_{RM} \approx 2.8 \times 10^6 \ V_b \sqrt{I_F |dI_F / dt|} & \text{(A)} \end{split}$$

where the avalanche breakdown voltage for a step junction,  $V_b$  is given by equation (2.3). The reverse recovery charge  $O_R$  is therefore given by

$$Q_R = \frac{1}{2} I_{RM} t_{rr} = 3.92 \times 10^{-12} V_b^2 I_F$$

(C) (4.6)

that is, the reverse recovery charge is proportional to the forward current, as shown in figure 5.9a for  $dI_F/dt > 100$  A/us.

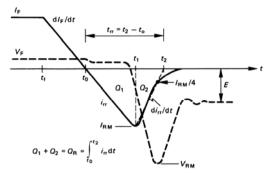

Figure 4.5 illustrates *snap-off* and *soft recovery* diode properties  $(S_r)$  which are characterised by the recovery  $di_{rr}/dt$  magnitude. The higher the value of  $di_{rr}/dt$ , the higher is the induced diode overshoot  $V_{RM}$  and it is usual to produce soft recovery diodes so as to minimise voltage overshoot  $V_{PM}$ , resulting from inductive ringing.

Reverse recovery properties are characterised for a given temperature, forward current  $I_F$ , and  $dI_F/dt$  as shown in figure 5.9.

Figure 4.5. Comparison of fast recovery diode di<sub>rr</sub>/dt characteristics of: (a) short current tail, producing snap-off (low S<sub>1</sub>) and (b) gradual current tail, producing soft recovery (high S<sub>1</sub>).

#### 4.2.3 Schottky diode dynamic characteristics

Being a minority carrier device, the Schottky barrier diode, both in silicon and silicon carbide, is characterised by the absence of forward and reverse recovery, plus the absence of any temperature influence on switching.

Forward recovery traits tend to be due to package and external circuit inductance. Reverse recovery is dominated by the barrier charging – a capacitive effect, which increases slightly with increased temperature, reverse di/dt, and  $I_F$ . The barrier charge requirements are significantly less than the highly temperature dependant minority carrier charge  $Q_o$ , associated with the bipolar pn junction diode. Unlike the pn diode, as Schottky junction charging occurs, the junction reverse bias voltage begins to increase immediately. Turn-off voltages are well controlled, less snappy, as the capacitor barrier junction acts like a capacitive turn-off snubber, as considered in chapter 8.3.

Whereas the transient performance is virtually independent of temperature, the static of forward and reverse I-V characteristics are highly temperature dependant. In the case of silicon carbide, the reverse leakage current increases by 4% IK, the reverse breakdown voltage decreases by -4% IK while a 0.45% IK increase in onstate voltage means die can be readily parallel connected. In contrast, it will be noticed in figure 2.2 that reverse breakdown voltage and leakage current of a bipolar junction diode, both have a positive temperature co-efficient.

#### 4.3 The bipolar, high-voltage, power switching npn transistor

The electrical properties of the high-voltage power switching npn transistor are related to and dominated by the wide low-concentration n collector region

employed to obtain high-voltage characteristics in all semiconductor devices. Many of the limitations and constraints on the MOSFET, IGBT, and the different thyristors are due to their parasitic bjt structures, which introduce undesirable BJT characteristics and mechanisms. It is therefore essential to understand the electrical characteristics and properties of the BJT if the limitations of other devices are to be appreciated.

#### 4.3.1 Transistor ratings

## 4.3.1i - BJT collector voltage ratings

The breakdown voltage ratings of a transistor can be divided into those inherent to the actual transistor ( $V_{ceo}$ ,  $V_{cbo}$ ) and those that are highly dependent on the external base circuit conditions ( $V_{ceo}$ ,  $V_{ces}$ ,  $V_{cev}$ ).

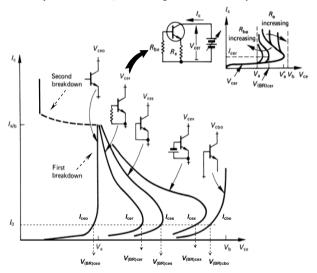

Figure 4.6 shows the various voltage breakdown modes of the BJT, which are defined as follows

- $V_{cbo}$  Collector to base voltage-current characteristics with the emitter open; that is,  $I_e = 0$ , where  $V_{(BB)cbo}$  is the collector to base breakdown voltage with  $I_e = 0$  and the collector current  $I_c$  specified as  $I_{cbo}$ .

- $V_{ceo}$  Collector to emitter characteristics with the base open circuit such that the base current  $I_b = 0$ , where  $V_{(BB)ceo}$  is the collector to emitter breakdown voltage with  $I_b = 0$  and  $I_c$  specified as  $I_{ceo}$ .

- $V_{ces}$  Collector to emitter characteristics with the base shorted to the emitter such that  $V_{be} = 0$ , where  $V_{(BR)ces}$  is the collector to emitter breakdown voltage with  $I_c$  specified as  $I_{ces}$ .

- $V_{cer}$  Collector to emitter characteristics with resistance R between the base and the emitter such that  $R_{be} = R$ , where  $V_{(BR)cer}$  is the collector to emitter breakdown voltage with  $I_c$  specified as  $I_{cer}$ .

- $V_{cev}$  Collector to emitter characteristics with reverse base to emitter bias  $V_{eb} = X$ , where  $V_{(BR)cex}$  is the collector to emitter breakdown voltage with  $I_c$  specified as  $I_{cex}$ .

Each breakdown voltage level and its relative magnitude can be evaluated.

I – BJT  $V_{(BR)cbo}$  - maximum collector-base voltage with the emitter open circuit The  $V_{(BR)cbo}$  rating is just less than the voltage  $V_b$ , where the base to collector junction breaks down because of avalanche multiplication, as illustrated in figure 4.6. The common base avalanche breakdown voltage  $V_b$  is determined by the concentration of the collector n-region,  $N_c$ /cc, and as its resistivity increases,  $V_b$  increases according to (equation (2.3))

$$V_b = 5.34 \times 10^{13} \times N_c^{-3/4} \tag{V}$$

It can be assumed that  $V_{(BR)cbo} \approx V_b$ .

2 – BJT  $V_{(BR)ceo}$  - maximum collector-emitter voltage with the base open circuit Avalanche multiplication breakdown of a common emitter connected transistor occurs at a collector voltage  $V_a$  when the common emitter amplification factor  $\beta$  becomes infinite. The gain  $\beta$ , from equation 3.4 and accounting for avalanche multiplication, is defined by

Power Electronics

$$\beta = \frac{\alpha_0 M}{1 - \alpha_0 M} \tag{4.8}$$

77

where M is the avalanche multiplication factor, which is collector junction voltage  $V_{cb}$  dependent, according to (equation 3.17)

$$M = 1 / \left( 1 - \frac{V_{cb}}{V_b} \right)^m \tag{4.9}$$

The factor m is empirically determined and is between 2 and 4 for the collectorbase doping profile of the high-voltage silicon npn transistor. The common base current amplification factor  $\alpha_0$  is for a voltage level well below any avalanche.

Figure 4.6. Relative magnitudes of npn transistor collector voltage breakdown characteristics, showing first and second breakdown.

At high  $V_{cb}$  voltages, near  $V_a$ , avalanche multiplication causes a high injection of hole carriers. Thus no base current is required and a  $\beta \to \infty$  condition effectively occurs. With such conditions, equation (4.8) indicates that  $\alpha_0 M \to 1$  which, upon substitution into equation (4.9), yields

$$V_a = V_b \sqrt[m]{1 - \alpha_0} \approx V_{(BR)ceo}$$

(V) (4.10)

$V_a$  becomes the common emitter avalanche breakdown voltage and  $V_{(BR)ceo}$  is

commonly called the collector emitter sustaining voltage,  $V_{ceo(sus)}$

It can be shown that

$$V_{(BR)cbo} > V_{(BR)cex} > V_{(BR)ces} > V_{(BR)cer} > V_{(BR)cer} > (4.11)$$

With low-gain BJTs,  $V_a$  is almost  $V_b$  in value, but with high-gain devices  $V_b$  may be 2 to 3 times that of  $V_a$ . Notice in figure 4.6 that negative resistance characteristics occur after breakdown, as is the case with all the base circuit-dependent breakdown characteristics.

The inserted diagram in figure 4.6 shows how base-emitter resistance affects collector-emitter voltage breakdown. Importantly, the breakdown voltage increases as the base-emitter resistance decreases. This is because the injection efficiency of the emitter is reduced. This shorting feature is exploited extensively in alleviating problems in the MOSFET, IGBT, and thyristor devices, and is discussed in the respective device sections.

#### 4.3.1ii – BJT safe operating area (SOA)

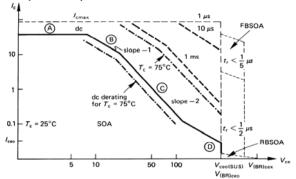

The safe operating area represents that electrical region where a transistor performs predictably and retains a high reliability, without causing device destruction or accelerated deterioration.

Deterioration or device destruction can occur when operating within the absolute maximum device ratings, as a result of second breakdown (s/b) or excessive thermal dissipation. Typical SOA characteristics are shown in figure 4.7. These collector characteristics are for a single pulse, of a given duration, such that the transistor operates in the linear region and at a case temperature of  $25^{\circ}$ C. The dc or continuous operation case has the most restrictive SOA curve, while a short single pulse of 1 us duration enables the full device I-V ratings to be exploited.

The SOA is basically bounded by the maximum collector  $I_{cmax}$  and the collector emitter breakdown voltage  $V_{(BR)cco}$ . In figure 4.7 it will be seen that four distinct operating region limits exist, viz., A to D.

- **A** Maximum collector current which is related to allowed current density in the leads and contacts and the minimum gain of the transistor. The maximum lead current is given by  $I = Kd^{2/3}$  where the diameter d is in mm and K depends on the type and length of wire. For lengths greater than 1mm, K = 160 for both copper and silver.

- **(B)** Maximum thermal dissipation, which is related to the absolute maximum junction temperature  $T_{j\max}$ , and the thermal resistance or impedance from the virtual junction to the case. In this thermally limited region, the collector power loss is constant and  $I_c = P V_c^{-1}$ . Thus the thermal limit gradient is -1, when plotted on logarithmic axes as in figure 4.7.

- ©Limit of forward second breakdown. This breakdown occurs when the local current density is too high and a hot spot is created which causes thermal runaway. The physical causes of the high current concentration phenomenon are a fall in electrical potential or instability of lateral temperature distribution in the base area. These occur as a consequence of base-width concentration non-uniformity, a faulty junction or improper chip

mounting. A typical s/b characteristic is shown in figure 4.6, and is characterised by a rapid drop in collector voltage to the low-impedance area after s/b. The s/b SOA limit can be modelled by  $I_{i,b} = PV^*$ , where n, the gradient in figure 4.7, ranges from 1.5 to 4 depending on the fabrication processes and structures that have been employed. S/b, with a forward-biased base emitter is usually characterised by a short circuit at the emitter periphery, since this area is more forward-biased than central regions because of lateral base resistance effects. S/b, with a reverse-biased base-emitter junction, occurs in the central emitter region because of current focusing to that area as a result of the same lateral base resistance effects.

Maximum collector voltage under worst case conditions. In switching applications the  $V_{(BR)cco}$  limit can be exceeded provided suitable base conditions exist. At turn-off, when the collector current has fallen below  $I_{cco}$  the collector supporting voltage can be increased from  $V_{(BR)cco}$  to  $V_{(BR)cco}$  if the proper reverse bias base emitter junction conditions exist. The SOA together with this small extension area form the *reverse bias SOA*. Turn-on in switching applications can take place from a  $V_{(BR)cco}$  condition, provided the collector current rise time is very short, usually much less than  $1 \mu s$ . As the rise time value decreases, the current that can be switched at turn-on increases. Under such conditions a significant portion of  $I_{cmax}$  can be switched from  $V_{(BR)cco}$ . The SOA together with this quite large switch-on extension area form the *forward bias SOA*, as shown in figure 4.7.

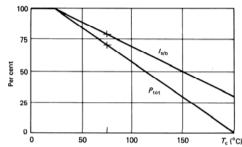

The SOA is usually characterised for a case temperature of 25°C. In practice much higher case temperatures are utilised and then the power and s/b SOA limits are modified with the aid of the derating curves of figure 4.8. At a given case temperature, above 25°C, power derating is greater than s/b derating. No derating is necessary for case temperatures below 25°C.

Figure 4.7. Safe operating area (SOA) bounds of an npn high-voltage power switching transistor including forward and reverse bias SOA. Temperature derating for a case temperature of 75°C is shown.

Figure 4.8. Power and second breakdown derating versus case temperature.

It is important to note that when a transistor is employed in a switching application, where the device is either cut-off or hard-on, the full SOA bounded by  $I_{\rm cmax}$  and  $V_{(BR){\rm ceo}}$  can usually be exploited. As indicated in figure 4.7, provided the collector switching times are of the order of a microsecond or less, no power or s/b derating need be factored. Design is based on total power losses, such that the maximum allowable junction temperature,  $T_{\rm jmax}$  is not exceeded. For high reliability and long device lifetime only one limit, either  $I_{\rm cmax}$  or  $V_{(BR){\rm ceo}}$ , should be exploited in a given application.

## 4.3.2 Transistor switching characteristics

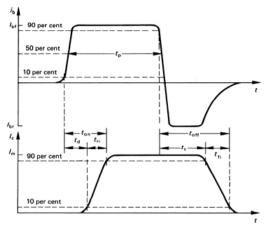

If a current pulse is supplied into the base of a common emitter connected transistor, as shown in figure 3.8, the resultant collector current waveform is as shown in figure 4.9. The collector voltage waveform is essentially collector load circuit dependent and therefore is not used to characterise transistor switching.

## 4.3.2i – BJT turn-on time: $t_{on} = t_d + t_{ri}$

Turn-on consists of a delay time  $t_d$  followed by a current rise time  $t_{ri}$ .

The delay time corresponds mainly to the charging of the base-emitter junction diffusion capacitance. The turn-on delay time can be significantly reduced by increasing the applied rate and magnitude of the forward base current  $I_{bf}$ .

The current rise time is related to the effective base zone width and, as the base charge increases because of the base current, the collector current increases.

#### 4.3.2ii – BJT turn-off time: $t_{off} = t_s + t_{fi}$

In order to cut-off a transistor from the saturated state, all the accumulated charges must be neutralised or removed from the base and from the lightly doped n' region of the collector. The turn-off process is started by removing the forward base current  $I_{bf}$ , and applying the reverse base current  $I_{br}$ . The excess minority carriers, namely holes, in the collector n' region are progressively reduced in the process of providing the collector current. The excess minority carriers in the base are removed by the reverse base current. The reverse base current does not influence the collector n' region recombination process. The period after the cessation of positive base current until the transistor enters the linear region is termed storage or saturation time,  $t_s$ . Generally, and undesirably, the larger the forward gain  $\beta_f$ , the greater the saturation time,  $t_s$ .

Figure 4.9. Defining transistor base and collector current switching times for turn-

Optimal turn-off occurs when the emitter junction cuts off, as a result of  $I_{br}$ , just as the collector junction cuts off and enters the linear region. Thus the collector current fall time can be decreased by increasing the reverse base current immediately after the collector junction has cut off.

In switching applications, operation in the linear region is to be avoided, or at least traversed rapidly, because of the associated high device power losses. Although in the saturated state, with  $I_{bf} >> I_c \ / \beta_f$ , minimum forward gain and losses, this state is not conducive to a rapid turn-off transition to the cut-off region. In switching applications, in order to increase turn-off speed (decrease  $t_a$  and  $t_f \beta_f$ ), the transistor may be held in the quasi-saturation region by reducing and

### 4.3.3 BJT phenomena

Although the BJT is virtually obsolete as a discrete power switching device for new circuit designs, it has been considered in some detail both in this chapter and chapter 3.2.1. This is because its operating electrical mechanisms explain the major limiting electrical operating factors of all controlled power switching devices

- mosfet: In chapter 3.2.2 the reverse conducting inherent body diode in the

MOSFET is part of a parasitic npn transistor. This BJT structure can

produce unwanted MOSFET dv/dt turn-on. Notice in figure 3.14a that the

source metallization overlaps the p<sup>+</sup> well, there-in producing a base to

emitter shunting resistor, as shown by R<sub>be</sub> in figure 3.14b. The emitter

shunts perform two essential functions, but inadvertently creates a nonoptimal diode.

- First, the shunt decreases the injection efficiency hence gain of the BJT, decreasing the likelihood of a drain dv/dt resulting in sufficient Miller capacitance current to turn-on the parasitic BJT, as considered in chapter 3.2.1.

- Second, by decreasing the BJT gain, the npn section voltage rating is increased from  $V_{cep}$  to  $V_{cep}$  as considered in section 4.3.1.

- igbt: In figure 3.16d the equivalent circuit of the IGBT has a parasitic pnpnpn thyristor structure. Once again, the emitter metallization (R<sub>be</sub>) shunts

the base to emitter of the npn BJT, helping to avoid latch-up of the SCR

section, as modelled by the derivation of equation (3.18). Also the

voltage rating of the npn section is increased from V<sub>ceo</sub> to V<sub>cer</sub>. Improved

thermal stability also results. Judicious profiling of the transistor sections

is essential.

- gto thyristor: All the electrical operating mechanisms of the SCR are

explainable in terms of BJT mechanisms, including turn-on, turn-off, and

thermal stability. Emitter shorts are used extensively to decrease gain,

increase thermal stability, and increase voltage ratings and are essential in

providing separation in the bi-directional conducting thyristor, as

considered in chapter 3.3.4. The GTO thyristor also uses emitter shorts in

order to achieve a stable device at turn-off as shown in figure 3.28.

An understanding of BJT electrical operating mechanisms is fundamental to the design and operation of semiconductor power switching devices, whether principally bipolar operating devices or unipolar devices which have bipolar parasitic structures.

#### .4 The power MOSFET

The main electrical attributes offered by power MOSFETs are high switching speeds, no second breakdown (s/b), and high impedance on and off voltage control. MOSFETs, along with IGBTs, have replaced the bipolar junction transistor due to their superior switching performance and simpler gate control requirements.

#### 4.4.1 MOSFET absolute maximum ratings

The basic enhancement mode power MOSFET structure and electrical circuit symbol are shown in figure 3.11. The SOA bounds shown in figure 4.10 is confined by four outer bounds.

**(A)** The n epitaxial layer concentration and thickness is the key parameter in specifying the drain high-voltage ratings, such as  $V_{ds}$  and  $V_{dg}$ , which increase with temperature at approximately  $\pm 0.1$  per cent/K, as shown in figure 3.13.

**(B)** One important rating feature of the power MOSFET is that it does not display the s/b that occurs with the bipolar transistor. Figure 4.10 shows the safe operating area for transistors, with the bipolar transistor s/b limitation area shaded. The physical explanation as to why MOSFETs do not suffer from s/b is based on the fact that carrier mobility in the channel decreases with increased temperature at -0.6 per cent/K. If localised heating occurs, the carrier mobility decreases in the region affected and, as a consequence, the localised current reduces. This negative feedback, self-protection mechanism forces currents to be uniformly distributed along the channel width and through the silicon die. This property is exploited when paralleling MOSFET devices. As a result of the enlarged SOA, the power MOSFET is generally a much more robust device than its bipolar counterpart. This region is thermally limited, as defined by  $I = P/V^{-1}$  giving the -1 slope in figure 4.10.

© The drain current rating is also related to the epitaxial properties. Its resistance specifies the  $I_a^2 R_{d_a(m)}$  power loss, which is limited by the junction to case thermal resistance,  $R_{\theta j \text{-c}}$ . The continuous, usable drain current above 25°C is thus given by

$$I_d = \sqrt{\frac{T_{j\text{max}} - T_c}{R_{ds(\text{on})} R_{\theta j \cdot c}}} \tag{A}$$

(b) When the MOSFET is on, with minimum drain voltage at maximum drain current, it operates in the resistive mode where the drain current is given by

$$I_d = \frac{1}{R_{def(n)}} V_{ds} \tag{A}$$

The SOA region at high currents and low voltages is thus characterised by a line of slope 1, on logarithmic axes, as shown in figure 4.10.

The gate to source voltage  $V_{\rm gs}$  controls the channel and the higher the value of  $V_{\rm gs}$ , the higher the possible drain current. The gate to source is a silicon dioxide dielectric capacitor which has an absolute forward and reverse voltage that can be impressed before dielectric breakdown. Typical absolute maximum voltage levels vary from  $\pm 10 \text{V}$  to  $\pm 40 \text{V}$ , as the oxide layer increases and capacitance

#### Characteristics of Power Semiconductor Switching Devices

advantageously decreases.

Figure 4.10. The safe operating area of the power MOSFET, which does not suffer second breakdown.

#### 4.4.2 Dynamic characteristics

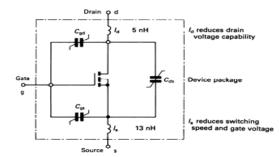

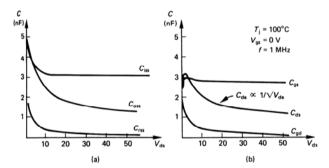

The important power MOSFET dynamic characteristics are inter-terminal voltagedependent capacitance and drain current-switching times. The various MOSFET capacitances are dominant in specifying switching times.

#### 4.4.2i – MOSFET device capacitances

Figure 4.11 shows an equivalent circuit for the power MOSFET, extracted from figure 3.14, which includes three inter-terminal, non-linear voltage-dependent capacitances  $C_{od}$ ,  $C_{os}$ , and  $C_{ds}$ . The magnitudes are largely determined by the size of the chip and the cell topology used. Therefore higher current devices inherently have larger capacitances. Electrically, these capacitances are strongly dependent on the terminal drain-source voltage.

Manufacturers do not generally specify  $C_{gd}$ ,  $C_{gs}$ , and  $C_{ds}$  directly but present input capacitance  $C_{iss}$ , common source output capacitance  $C_{oss}$ , and reverse transfer capacitance  $C_{rss}$ . These capacitances, as a function of drain to source voltage, are shown in figure 4.12a. The manufacturers' quoted capacitances and the device capacitances shown in figure 4.12b are related according to

$$C_{ts} = C_{gt} + C_{gd};$$

$C_{dt}$  shorted (F) (4.14)

$C_{rs} = C_{gd}$  (F) (4.15)

$$C_{rss} = C_{gd} \tag{F}$$

Power Electronics

$$C_{oss} = C_{ds} + \frac{C_{gs} \cdot C_{gd}}{C_{gs} + C_{gd}}; \qquad C_{gs} \text{ shorted}$$

$$\approx C_{ds} + C_{gd} \qquad (F)$$

The measurement frequency is usually 1 MHz and any terminals to be shorted are connected with large, high-frequency capacitance, so as to present a short circuit at the measurement frequency.

Device capacitances are predominant in specifying the drain current switching characteristics, particularly  $C_{ed}$  with its large capacitance variation at low drain voltage levels.

Figure 4.11. MOSFET equivalent circuit including terminal voltage dependent capacitance and inductance for the TO247 package.

Figure 4.12. MOSFET capacitance variation with drain-to-source voltage: (a) manufacturers' measurements and (b) inter-terminal capacitance values.

#### 4.4.2ii - MOSFET switching characteristics

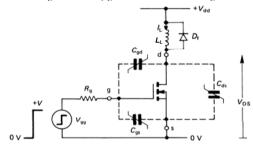

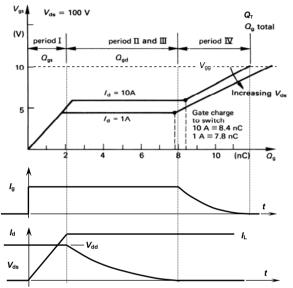

The simple MOSFET circuit with an inductive load  $L_L$  in figure 4.13, can illustrate how device capacitances influence switching. The MOSFET gate is driven from a voltage source whose output impedance is represented by R<sub>a</sub>, which also includes any MOSFET gate series internal resistance. The dc input resistance of a power MOSFET is in excess of 10<sup>12</sup> Ohms and when used as a switch, the power required to keep it on or off is negligible. However energy is required to change it from one state to another, as shown in figure 4.14. This figure shows the relationship between gate charge, gate voltage, and drain current for a typical MOSFET. The initial charge  $Q_{ex}$  is that required to charge the gate-source capacitance and  $Q_{ed}$  is that required to supply the drain-gate Miller capacitance. For a given gate charging current, switching speed is proportional to gate voltage. The gate charge required for switching, and hence switching speed, is not influenced significantly by the drain current magnitude, and not at all by the operating temperature. The switching speed is directly related to time delays in the structure because of the channel transit time of electrons. External to the device the switching time is determined by the energy available from the drive circuit. A gate drive design example based on gate charge requirement is presented in chapter 7.1.2.

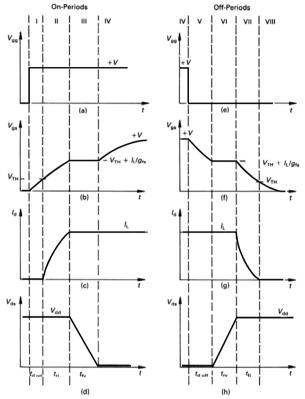

The switching transients can be predicted for an inductive load, when the load is the parallel inductor and diode, with no stray unclamped inductance, as shown in figure 4.13. It is assumed that a steady load current  $I_L$  flows. The various turn-on and turn-off periods shown in figure 4.15 are related to the sequential charging periods shown in figure 4.14. Any gate circuit inductance is neglected.

Figure 4.13. MOSFET basic switching circuit used to demonstrate current switching characteristics.

## 1 - MOSFET turn-on

**Period I -** turn-on delay,  $t_{d \text{ on }}$

The gate voltage rises exponentially to the gate threshold voltage  $V_{TH}$  according to equation (4.17), that is

$$V_{ex}(t) = V_{ex} \left[ 1 - e^{-t/C_{in} R_g} \right]$$

(V) (4.17)

where  $C_{in}$ , the gate input capacitance is approximated by  $C_{gd} + C_{gs}$ , or  $C_{iss}$ . The

drain voltage remains unchanged, that is, it supports the supply voltage  $V_{dd}$  and no MOSFET drain current flows. The turn-on delay time is given by

$$t_{d \text{ on }} = C_{in} R_{g} \, \ell n \left( 1 - \frac{V_{TH}}{V_{gg}} \right)^{-1}$$

(s) (4.18)

Equations (4.17) and (4.18) can be modified to account for a negative initial gate voltage (as presented in Appendix 4.1), a condition which increases the turn-on delay time. but increases input noise immunity.

Figure 4.14. Typical relationships between gate charge, voltage, and current and magnitude of drain current and voltage being switched.

#### **Period II** - current rise, $t_{ri}$

Drain current commences to flow in proportion to the gate voltage as indicated by the transconductance characteristics in figure 3.12a. The gate voltage continues to rise according to equation (4.17). The drain voltage is clamped to the rail voltage  $V_{dd}$  and the drain current rises exponentially to the load current level  $I_L$ , according to

$$I_d(t) = g_{fs} \left( V_{gg} - V_{TH} \right) \left[ 1 - e^{-t/R_g C_{in}} \right]$$

(A) (4.19)

The current rise time  $t_{ri}$  can be found by equating  $I_d = I_L$  in equation (4.19).

#### Characteristics of Power Semiconductor Switching Devices

Period III - voltage fall, to

When the drain current reaches the load current level, the drain voltage will fall from  $V_{dd}$  to the low on-state voltage. This decreasing drain voltage produces a feedback current via  $C_{ed}$  to the gate, which must be provided by the gate drive. This feedback mechanism is called the *Miller effect* and the effective gate input capacitance increases to  $C_{in} = C_{iss} + (1 - A_v)C_{ed}$  where  $A_v = \Delta V_{ds}/\Delta V_{es}$ . For a constant load current, from figure 3.12a, the gate voltage remains constant at

$$V_{gg} = V_{TH} + I_L / g_{fg}$$

(V) (4.20)

as shown in figure 4.15b.

Since the gate voltage is constant, the Miller capacitance  $C_{ad}$  is charged by the constant gate current

$$I_{s} = \frac{V_{ss} - V_{gs}}{R_{s}} = \frac{V_{ss} - (V_{TH} + I_{L}/g_{fs})}{R_{s}}$$

(A) (4.21)

and the rate of change of drain voltage will be given by

$$\frac{dV_{gd}}{dt} = \frac{dV_{ds}}{dt} = \frac{I_g}{C_{od}} \tag{V/s}$$

that is

$$V_{di}(t) = V_{dd} - \frac{I_g}{C}t$$

(V) (4.23)

The drain voltage decreases linearly in time and the voltage fall time is decreased by increasing the gate current. Assuming a low on-state voltage, the voltage fall time  $t_{fv}$  is given by

$$t_{fr} = V_{dd} C_{red} / I_{re}$$

(s) (4.24)

#### Period IV

Once the drain voltage reaches the low on-state voltage, the MOSFET is fully on and the gate voltage increases exponentially towards  $V_{gg}$ .

#### 2 - MOSFET turn-off

**Period V** - turn-off delay,  $t_{d \text{ off}}$

The MOSFET is fully on, conducting the load current  $I_L$ , and the gate is charged to  $V_{gg}$ . The gate voltage falls exponentially from  $V_{gg}$  to  $V_{TH} + I_L / g_{fi}$  according to  $V_{gg}(t) = V_{gg} e^{-t/R_g C_{fig}}$  (V)

$$V_{a}(t) = V_{a} e^{-t/R_g C_{in}}$$

(V) (4.25)

in a time given by

$$t_{d \text{ off}} = R_s C_{in} \, \ell n \frac{V_{ss}}{V_{TH} + I_L / g_{fi}}$$

(s) (4.26)

This delay time can be decreased if a negative off-state gate bias is used. The drain conditions are unchanged.

**Period VI** - voltage rise,  $t_{rv}$

The drain voltage rises while the drain current is fixed to the load current level,  $I_L$ . Accordingly the gate voltage remains constant and the gate current is given by

Power Electronics

$$I_{g} = \frac{V_{m_{\ell}} + I_{L}/g_{j_{\ell}}}{R}$$

(A)

89

This current discharges the Miller capacitance according to

$$\frac{dV_{ds}}{dt} = \frac{dV_{ds}}{dt} = \frac{I_s}{C_{col}}$$

(V/s)

Figure 4.15. Distinct switching periods of the MOSFET with an inductive load at: (a) (b) (c) (d) comprising turn-on; (e) (f) (g) (h) forming turn-off.

$$V_{d}(t) = \frac{I_g}{C_{d}} t \tag{V}$$

where the low on-state voltage has been neglected.

The drain voltage rises linearly to the supply  $V_{dd}$ . The voltage rise time  $t_{rv}$  is given by

$$t_{rr} = \frac{C_{gd} V_{dd}}{I_{g}}$$

(s) (4.30)

and is decreased by increasing the gate reverse current magnitude.

#### Period VII - current fall, to

When the drain voltage reaches the supply rail, the load current in the MOSFET begins to decrease, with load current being diverted to the diode  $D_{\rm f}$ .

The gate voltage decreases exponentially according to

$$V_{-}(t) = (V_{ru} + I_{L}/g_{o}) e^{-t/R_{g}C_{in}}$$

(V) (4.31)

and is mirrored by the drain current

$$I_{s}(t) = (I_{s} + g_{s}V_{TH})e^{-t/R_{g}C_{in}} - g_{s}V_{TH}$$

(A) (4.32)

The current fall time  $t_{fi}$  is given by  $I_d = 0$  in equation (4.32) or when the gate-source voltage reaches the threshold voltage, that is, from equation (4.31)

$$t_{ji} = R_{g} C_{iii} \ell n \left( 1 + \frac{I_{L}}{g_{ji} V_{TH}} \right)$$

(s) (4.33)

#### Period VIII - off-state

The MOSFET drain is cut-off and the gate voltage decays exponentially to zero volts according to

$$V_{ox}(t) = V_{TH} e^{-t/R_g C_{in}}$$

(V) (4.34)

Based on the total gate charge  $Q_T$  delivered by the gates source  $V_{\rm gg}$ , shown in figure 4.14, the power dissipated in the MOSFET internal gate resistance, hence contributing to device losses, is given by

$$P_{G}(R_{\text{int}}) = V_{gg} Q_{T} f_{s} \frac{R_{Gint}}{R_{Gint} + R_{Gext}}$$

(W) (4.35)

#### 4.5 The insulated gate bipolar transistor

## 4.5.1 IGBT switching

The IGBT gate charge characteristics for switching and the switching waveforms are similar to those of the MOSFET, shown in figures 4.14 and 4.15 respectively, whilst the I-V on and off state characteristics are similar to the BJT. The collector switching characteristics depend on the injection efficiency of the collector p<sup>+</sup> emitting junction. The higher the injection efficiency, the higher the pnp transistor section gain and the lower the on-state voltage. The poorer the injection efficiency, the more the characteristics resemble a MOSFET.

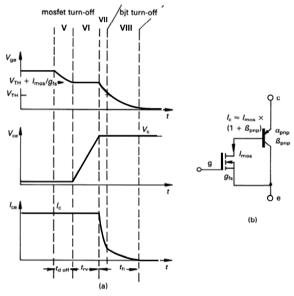

The turn-on waveforms and mechanisms are essentially those for the MOSFET shown in figure 4.15. Figure 4.16 shows IGBT turn-off which has components due to MOSFET and BJT action. As with the MOSFET, distinct turn-off stages exist when switching an inductive load.

**Period V** - turn-off delay,  $t_{d \text{ off}}$

The gate voltage falls to a level determined by the gate threshold,  $V_{TH}$ , the forward transconductance,  $g_{c}$  and the MOSFET section current level.

#### **Period VI** - voltage rise, $t_{rv}$

As the collector voltage rises the collector current remains constant, hence the gate voltage remains constant while charging the Miller capacitance. For a high gain pnp section the voltage rise time is virtually independent of gate resistance, while for an IGBT closely resembling a MOSFET the voltage rise is gate current magnitude dependent.

#### **Period VII** - current fall, $t_{\theta}$

The current falls in two sections, the first, phase VII, due to MOSFET action, as are the previous two phases (periods V and VI). As with the conventional MOSFET the current falls rapidly as the MOSFET section current, shown in figure 4.16b reduces to zero.

Figure 4.16. IGBT (a) turn-off waveforms and (b) equivalent circuit during turnoff.

With the gate voltage at the threshold level, the pnp transistor section turns off in a  $V_{ceo}$  mode, phase VIII. A relatively low-magnitude, lengthy current tail results which is dependent on the pnp transistor section minority carrier lifetime in the n base and the injection efficiency of the  $p^+$  collector region.

The switching frequency and current rating of an IGBT are both limited by the minimum of the package dissipation limit (as with any other semiconductor device) and a factor solely dependant on the switching times at turn-on and turn-off. As the switching frequency increases, the current rating decreases. The MOSFET upper frequency is restricted solely by losses, that is, temperature.

#### 4.5.2 IGBT short circuit operation

Under certain electrical conditions the IGBT may be subjected to short circuits, and safely turned off with out damage. Two different short circuit conditions are characterised:

- I IGBT turn-on into a pre-existing load short circuit

- II subsequent to IGBT turn-on, a short circuit load condition occur during the on-state period

## I Pre-existing short circuit at turn-on

The collector electrical characteristics are determined by the gate drive parameters and conditions. As the collector voltage falls, the collector current *di/dt* is determined by the stray inductance, characterised at less than 25uH. In this fault mode the IGBT is characterised for up to ten times the rated current, provided the IGBT is turned off within 10us, but at a slower rate than normal.

#### II Short circuit arising during the normal on-period

When a load short circuit occurs during the IGBT on period, the collector current rises rapidly and is determined by to the supply voltage  $V_s$  and stray inductance  $L_s$  according to  $di_{rise}/dt = V_s/L_s$ . The collector voltage de-saturates and as the collector voltage rise towards the supply  $V_s$  the resultant dv/dt produced a Miller capacitance charging current, which flows into the gate circuit. Depending on the gate drive impedance, the gate voltage rises which allows higher collector current.

When turn-off is initiated, by reducing the gate voltage to below the threshold level, the resultant collector current fall produces a high voltage across the stray inductance,  $V = L_s \, di_{fall} / dt$ , which adds to the collector voltage which is already near the supply rail  $V_s$ . Because of this over voltage, this mode of short circuit turn-off is more than turning off into a pre-existing short circuit.

The maximum allowable short circuit current at turn-off is dependant on the gate voltage and reduces from ten times rated current at a gate voltage of 18V down to five time rated current at 12V. The short circuit must be commutated within 10us at a slower than normal rate so as to ensure the over voltage due to stray inductance remains within rated voltage limits. Repetitive short circuits are restricted to a frequency of less than one Hertz and can only accumulate to 1000 before device deterioration: both mechanical and electrical.

Stress during the fault period can be reduced if the gate voltage is clamped so that it cannot rise during the Miller capacitance charge period. A Zener diode (and reverse series diode if reverse gate bias is used) across the gate to emitter provides low inductance gate voltage clamping, but the Zener standby to clamping voltage ratio of 1:1.4 limits clamping effectiveness. The preferred method is to clamp the gate to the gate supply voltage by a Schottky diode between gate (diode anode) and gate positive supply (diode cathode). Judicious gate supply ceramic capacitance decoupling will minimise loop inductance which otherwise would deteriorate clamping effectiveness

A difficulty arises when attempting to utilise the 10us short circuit capabilities of the IGBT. To improve device robustness, short circuit turn-off is staged, or slowed down. It is prudent to utilise the over current capability of the IGBT in order to improve nuisance tripping or brief capacitor charging which are not true faults. A difficulty arises when a demand pulse is significantly less than 10us. The gate drive must be able to cater for sub 10us pulses with normal turn-off yet differentiate 10us delayed slow turn-off when a short circuit fault is serviced.

#### 4.6 The thyristor

Most of the thyristor ratings and characteristics to be considered are not specific to only the silicon-controlled rectifier, although the dynamic characteristics of the gate turn-off thyristor are considered separately.

## 4.6.1 SCR ratings

The fundamental four layer, three junction thyristor structures and their basic electrical properties were considered in chapter 3.3.

#### 4.6.1i - SCR anode ratings

Thyristors for low-frequency application, such as in 50-60 Hz ac supply systems, are termed *converter-grade* thyristors. When a higher switching frequency is required, so-called *gate commutated* devices like the GTO and GCT are applicable. Such devices sacrifice voltage and current ratings for improved self-commutating canability

The repetitive peak thyristor voltage rating is that voltage which the device will safely withstand in both the forward off-state  $V_{DRM}$ , and reverse direction  $V_{RRM}$ , without breakdown. The voltage rating is primarily related to leakage or blocking current  $I_{RRM}$  and  $I_{DRM}$  respectively, at a given junction temperature, usually 125°C. Since blocking current doubles with every 10K rise in junction temperature  $T_{J_p}$  power dissipation increases rapidly with  $T_{J_p}$  which may lead to regenerative thermal runaway, turning the device on in the forward direction.

Current related maximum ratings reflecting application requirements include

- peak one cycle surge on-state current I<sub>TSM</sub>

- repetitive and non-repetitive di/dt

- I<sup>2</sup>t for fusing.

The maximum junction temperature can be exceeded during non-recurrent over-

Power Electronics

95

current cycles. The maximum non-repetitive on-state surge current is generally quoted for one 10 millisecond sinusoidal period at  $T_{j\max}$ . Any non-recurrent rating can be tolerated only a limited number of times before failure results. Such non-recurrent ratings are usually specified to allow fuse and circuit breaker short-circuit protection. The  $I^2t$  rating for a 10ms period is another parameter used for fuse protection, where I is non-repetitive rms current.

If the device is turned on into a fault the initial current-time relationship, di/dt, during turn-on must be within the device's switching capability. In cases where the initial di/dt is rapid compared with the active area-spreading velocity of 50  $\mu$ m/ $\mu$ s, local hot spot heating will occur because of the high current densities in those areas that have started to conduct

A repetitive *di/dt* rating is also given for normal operating conditions, which will not lead to device deterioration. This repetitive *di/dt* rating will be specified for a given initial blocking voltage and peak forward current. Certain gate drive conditions are specified and the device must survive for 1000 hours.

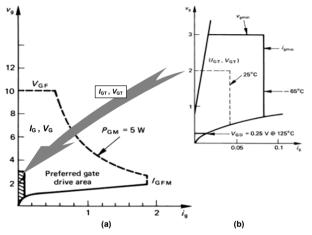

Figure 4.17. Thyristor gate ratings illustrating: (a) the preferred operating region and (b) minimum gate requirements and their temperature dependence.

#### 4.6.1ii - SCR gate ratings

The gate ratings usually specified are

- peak and mean gate power,  $P_{GM}$  and  $P_{G}$

- peak forward and reverse gate to cathode voltage, V<sub>GFM</sub> and V<sub>GRM</sub>

- peak forward gate current, I<sub>FMG</sub>.

These gate ratings are illustrated in figure 4.17. The peak gate power rating is obtained by using a low duty cycle pulse, with a mean power that does not exceed

$P_G$ . The reverse gate voltage limit,  $V_{GRM}$ , is specified by the avalanche voltage breakdown limit of the reverse-biased gate-to-cathode junction. Figure 4.17 not only shows limit ratings, it also indicates the preferred gate voltage and current, and the minimum requirements which will ensure turn-on at different junction temperatures.

#### 4.6.2 Static characteristics

The static anode voltage-current characteristics of a thyristor are very similar to those of a diode. Gate commutated thyristors tend to have higher on-state voltages for a given current than comparable converter-grade devices. This higher on-state voltage is one of the trade-offs in improving the switching performance.

#### 4.6.2i - SCR gate trigger requirements

Below a certain gate voltage, called the *gate non-trigger voltage*  $V_{GD}$ , the manufacturer guarantees that no device will trigger. This voltage level is shown in figure 4.17b. The shaded insert area in figure 4.17a (figure 4.17b) contains all the possible minimum trigger values  $(I_{GT}, V_{GT})$  for different temperatures, that will result in turn-on. The gate requirements  $(I_{GT}, V_{GT})$  have a negative temperature coefficient as indicated in figure 4.17b. To ensure reliable turn-on of all devices, independent of temperature, the trigger circuit must provide a de signal  $(I_G, V_G)$  outside the shaded area. This area outside the uncertainty area, but within the rating bounds, is termed the *preferred gate drive* area.

An increase in anode supporting voltage tends to decrease the gate drive requirements. But if the gate signal is a pulse of less than about  $100\mu_S$ , the turn-on  $(I_G, V_G)$  requirement is increased as the pulse duration is decreased. The gate current increase is more significant than the voltage requirement increase. Typically, for a pulse reduced from  $100\mu_S$  to  $1\mu_S$ , the voltage to current increase above the original requirement is 2:10 respectively. This increased drive requirement with reduced pulse time is accounted for by the fact that some of the initial gate p-region charge recombines. When the free charge reaches a certain level the device triggers. Thus, to get the required charge into the gate in a relatively short time compared with the recombination time requires higher current, and hence higher voltage, than for dc triggering.

## 4.6.2ii - SCR holding and latching current

If the on-state anode current drops below a minimum level, designated as the holding current  $I_H$ , the thyristor reverts to the forward blocking state. This occurs because the loop gain of the equivalent circuit pnp-npn transistors falls below unity and the regenerative hold-on action ceases. The holding current has a negative temperature coefficient; that is, as the junction temperature falls, the device holding current requirement increases. The holding current is typically about 2% of the rated anode current.

A somewhat higher value of anode on-state current than the holding current is required for the thyristor to latch on initially. If this higher value of anode *latching current I\_L* is not reached, the thyristor will revert to the blocking state as soon as the gate trigger signal is removed. After latch-on, however, the anode current may

be reduced to the holding current level, without turn-off occurring. These two static current properties are shown in the *I-V* characteristics in figure 3.21. With inductive anode circuits, it is important to ensure that the anode current has risen to the latching current level before the gate turn-on signal is removed. Continuous gate drive avoids this inductive load problem but at the expense of increased thyristor gate power losses.

#### 4.6.3 Dynamic characteristics

The main thyristor dynamic characteristics are the turn-on and turn-off switching intervals, which are associated with the anode and gate circuit interaction.

#### 4.6.3i-SCR anode at turn-on

Turn-on comprises a delay time  $t_d$  and a voltage fall time  $t_{fi}$ , such that the turn-on time is  $t_{cn} = t_d + t_{fi}$ .

The turn-on delay time for a given thyristor decreases as the supporting anode voltage at turn-on is increased. The delay time is also decreased by increased gate current magnitude. The gate p-region width dominates the high gate current delay time characteristics while carrier recombination is the dominant factor at low gate current levels.

The anode voltage fall time is the time interval between the 90 per cent and 10 per cent anode voltage levels. The associated anode current rise characteristics are load dependent and the recurrent *di/dt* limit must not be exceeded.

As introduced in chapter 3.3.1, a thyristor can be brought into conduction by means of an anode impressed dv/dt, called  $static\ dv/dt$  capability, even though no gate current is injected. The anode voltage ramp produces a displacement current according to i = dQ/dt as the central junction scl charges and its width increases. The resultant displacement current flows across the cathode and anode junctions causing emission and, if sufficient in magnitude, turn-on occurs. Static dv/dt capability is an inverse function of device junction temperature and is usually measured at  $T_{max}$ .

#### 4.6.3ii - SCR anode at turn-off

As analysed in chapter 3.3.1, once a thyristor is turned on, it remains latched-on provided that

- the holding current remains exceeded

- · it is forward biased.

If the supply voltage is ac, a thyristor will turn off after the supply voltage has reversed and the anode current attempts to reverse. The thyristor is thus reverse-biased and this turn-off process is called *line commutation* or *natural commutation*. If the supply voltage is dc and the load is a series *L-C* resonant circuit, the anode current falls to zero when the capacitor is charged. The load current falls below the holding current level and the SCR turns off. This is termed *load commutation*.

In thyristor applications involving dc supplies and resistive/inductive loads, a thyristor once on will remain on. Neither the supply nor the load is capable of reducing the anode current to below the holding current level, or producing a reverse bias across the thyristor. Such a thyristor can be turned off only if the anode current is interrupted or forced below the holding current level. External

circuitry, called a *commutation circuit*, is employed to accomplish turn-off, by reverse-biasing the thyristor and reducing the anode current to near zero. This external turn-off approach, now obsolete, is called *forced commutation*. The gate turn-off thyristor eliminates the need for this external commutation circuitry since the GTO can be commutated from its gate. A topological variation of the forced commutated circuitry method is called *resonant link commutation*.

#### 4.7 The gate turn-off thyristor

In essence, the gate turn-off (GTO) thyristor has similar ratings and characteristics to those of the conventional converter grade SCR, except those pertaining to turn-off. Both GTO turn-on and turn-off are initiated from the gate, hence the power-handling capabilities of the GTO gate are much higher than those of SCR devices.

#### 4.7.1 Turn-on characteristics

Because of the higher p1 gate region concentration, the GTO holding current level and gate trigger requirements are somewhat larger than those of the conventional SCR. Higher anode on-state voltages also result.

At low anode current levels, a steep trailing edge at the end of the gate on-pulse may cause the GTO to unlatch even though the anode current is above the dc holding current level. For this reason, together with the fact that the cathode comprises many interdigitated islands, a continuous, dc gate on-drive is preferred. Continuous gate current prevents any cathode islands from falling out of conduction should the anode current be reduced to near the holding current level. If cathode islands should turn off prematurely and the anode current subsequently rise, the GTO no longer has its full current handling capability and it could overheat, leading to device destruction.

With very high voltage GTO's, turn-on is like that of a high voltage npn transistor which has low gain, limiting the initial rate of rise of anode current, until the regenerative latching action has occurred. Hence an initial, high current of up to six times the steady-state gate requirement is effective for a few microseconds.

#### 4.7.2 Turn-off characteristics

Before commencing turn-off, a minimum on-time of tens of microseconds must be observed so that the principal current may distribute uniformly between the cathode islands. This is to ensure that all cells conduct, such that turn-off occurs uniformly in all cells, rather than being confined to a few cells, where the current to be commutated may be higher than individual cells can survive.

The anode current of a GTO in the on-state is normally turned off via a low voltage, negative gate current  $I_{RG}$ . The negative gate current  $I_{GG}$ , which is just sufficient to turn-off the on-state current  $I_T$  is defined as the minimum turn-off current. Turn-off amplification (equation 3.21) is defined as

$$\beta_o = I_{TGO} / I_{GO} \tag{4.36}$$

where  $\beta_O$  is related to the internal construction of the GTO.

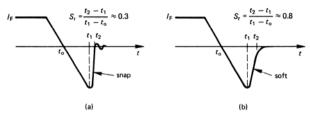

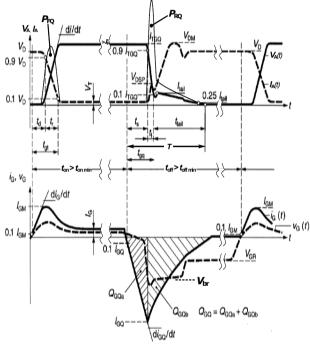

Figure 4.18 illustrates typical gate and anode turn-off waveforms for the GTO.

Application of reverse gate current causes the anode current to reduce after a delay period  $t_s$ . This delay time is decreased as the reverse gate current  $di_{GO}/dt$  increases; that is, as  $I_{RGM}$  increases and  $t_s$  decreases. Increased anode on-state current or junction temperature increases the delay time.

The reverse gate current prevents cathode injection and the anode current rapidly falls to the storage current level,  $I_{tail}$ . The subsequently slow current fall time, t<sub>trill</sub>, is due to charges stored in regions other than the gate and cathode that are not influenced by the reverse gate current and must decrease as a result of natural recombination. Anode n<sup>+</sup> shorts are used to accelerate the recombination process, reducing both storage current and storage time, but at the expense of reverse blocking ability and on-state voltage. Avalanche of the cathode junction (typically -20V) is acceptable on turn-off for a specified time. Reverse gate bias should be maintained in the off-state in order to prevent any cathode injection.

Figure 4.18. Schematic representation of GTO thyristor turn-off waveforms.

After turn-off some dispersed charges still exist. A minimum off-time of the order of tens of microseconds is needed for these charges to recombine naturally. This time increases with increased blocking voltage rating. If a turn-on were to be initiated before this recombination is complete, the area of un-combined charge will turn-on first, resulting in a high di/dt in a confined area, which may cause a hot spot and possibly destruction.

During the storage and fall time, power loss  $P_{RO}$  occurs as illustrated in figure 4.18 and is given by

$$P_{RQ} = \frac{1}{T} \int_{0}^{T} V_{A}(t) I_{A}(t) dt \qquad (W)$$

(4.37)

where  $T = t_{oa} + t_{tail}$ .

The actual anode voltage turn-off waveform is dependent on the load circuit. Care is needed in preventing excessive loss at turn-off, which can lead to device destruction. One technique of minimising turn-off loss is to increase the rate at which the reverse gate current is applied. Unfortunately, in reducing the turn-off time, the turn-off current gain  $\beta_0$  is decreased, from typically 25 to 3. The anode turn-off voltage  $V_{s}(t)$  in figure 4.18 assumes a capacitive turn-off snubber is used. Such a switching aid circuit is not essential with the GCT, which uses unity reverse gain at turn-off, as considered in chapter 3.3.5.

#### Appendix: Effects on MOSFET switching of negative gate drive

The effects of negative gate voltage on MOSFET turn-on and turn-off delays which was analysed in section 4.4.2 are given by

$$V_{gg}(t) = (V_{gg} - V_{gg}) [1 - e^{-t/C_{in} R_g}] + V_{gg}.$$

(V) (4.38)

$$t_{d \text{ on }} = R_{g} C_{in} \ \ell n \frac{V_{gg} - V_{gg}}{V_{gg} - V_{gg}}$$

(s) (4.39)

$$V_{gs}(t) = (V_{gg} - V_{gg}) e^{-t/R_g C_{in}} + V_{gg}$$

(V) (4.40)

$$t_{d \text{ off}} = R_g C_{in} \, \ell n \frac{V_{gg} - V_{gg}}{V_{TH} + I_L / g_{fi} - V_{gg}}$$

(s) (4.41)

## Reading list

See chapter 3 reading list